# **XCVR Design Training**

Peter Schepers High Speed Specialist November 2012

© 2012 Altera Corporation—Public

# Agenda

- Transceiver Architecture

- Clock Recovery and Jitter Tracking

- Transmitter PLL

- Transceiver Design

- Transceiver Reconfiguration

- Demo Design Using Reconfiguration

- Signal Conditioning and Best Practices for Link Training

- Signal Integrity Simulation (with Demo)

- Transceiver Toolkit (with Demo)

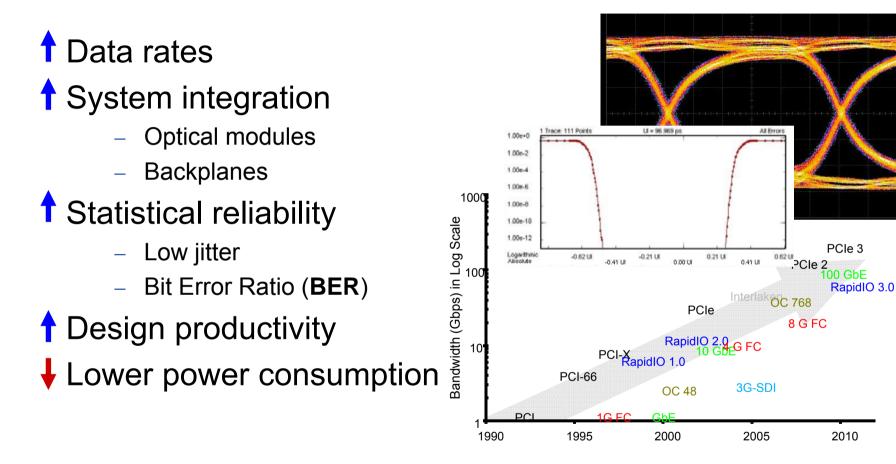

# **Transceiver Design Trends & Challenges**

### Altera's innovation address the challenges of next generation transceiver design

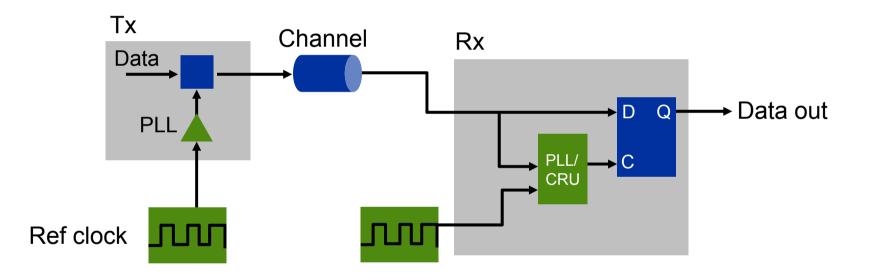

# What is a Transceiver?

- Combination transmitter/receiver used when sending high-speed digital data/control signals across physical medium

- Board traces

- Backplane

- Optical fiber

- CAT5 cable

- Used in the PHY (physical) layer of the OSI model

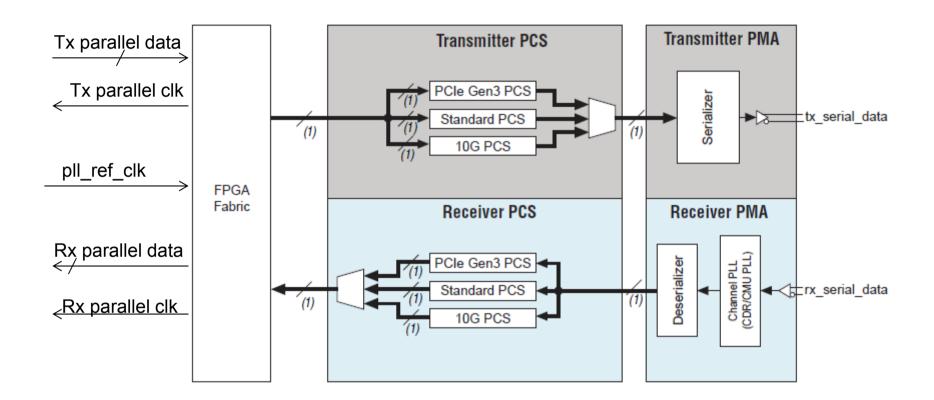

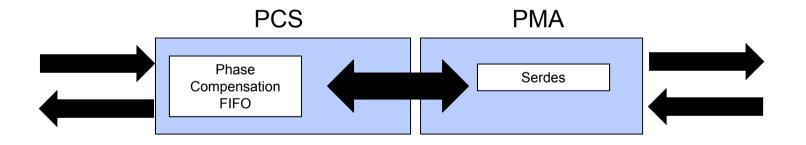

- Made up of the physical coding sub-layer and physical medium attachment

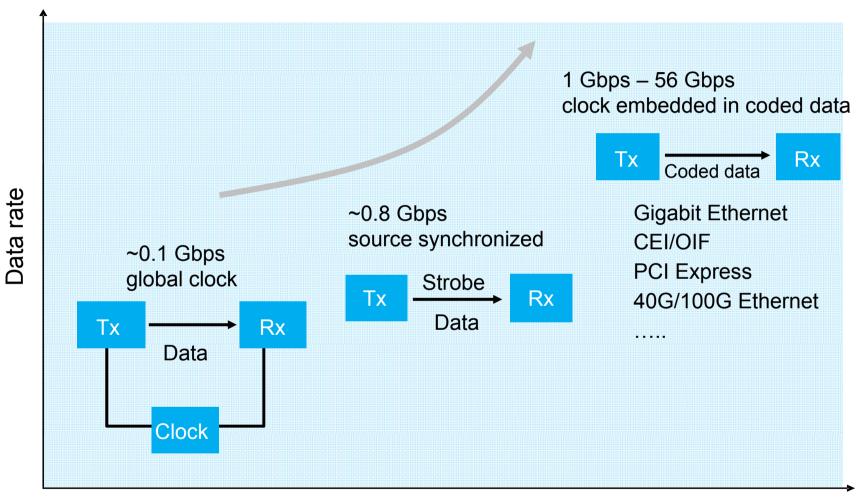

# **Serial Communication**

Ref clock

# What are transceivers

transmit and receive parallel data on a serial link

© 2012 Altera Corporation Public

# **Definitions**

- Media Access Controller (MAC)

- Assembles packets to be transmitted across link

- Disassembles packets received from across link

- Handles error and fault messages from link

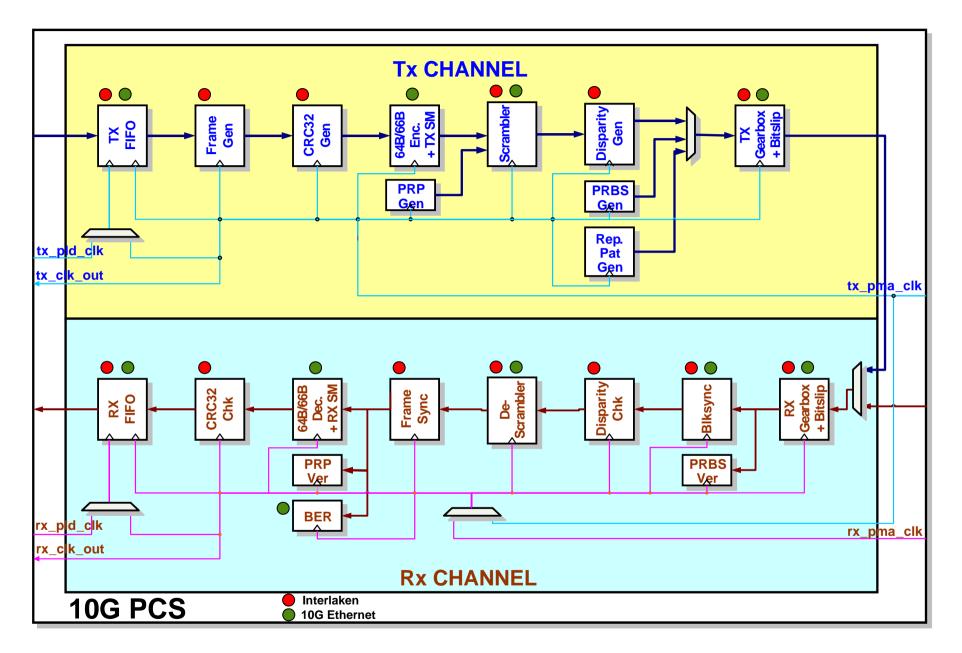

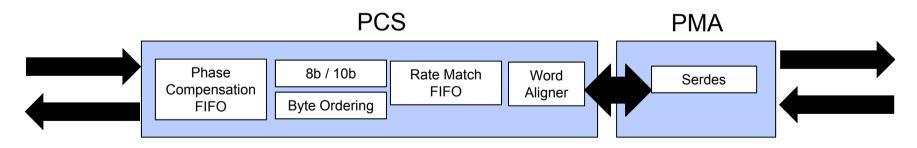

- Physical Coding Sub-Layer (PCS)

- Digital logic that prepares and formats data for transmission across a physical medium type or restores received data to original form

- Detects link errors

- Ex. Encoding, decoding, scrambling, descrambling

- Physical Medium Attachment (PMA)

- Converts digital data to serial analog stream or reverse

- Connects to physical medium

- Ex. Parallel to serial conversion

# **28-nm Device Families**

- Cyclone V

- Arria V

- Stratix V

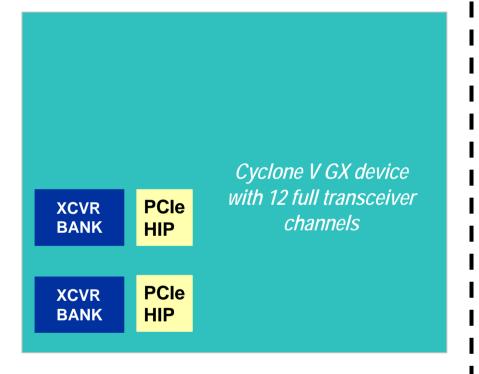

# **Cyclone V FPGA Family**

*Opening Up Design Possibilities*

|                                                           | Lowest<br>cost and power                                                                                               | 3G transceivers                                                                                        | 5G transceivers                                                                         |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| atera.<br>Cyclone V                                       | Optimized for<br>lowest system<br>cost and power<br>for a wide<br>spectrum of<br>general logic and<br>DSP applications | Optimized for<br>lowest cost and<br>power for 614<br>Mbps to 3.125<br>Gbps transceiver<br>applications | FPGA industry's<br>lowest cost and<br>power for 5.0<br>Gbps transceiver<br>applications |

| FPGA                                                      | E Variant                                                                                                              | GX Variant                                                                                             | GT Variant                                                                              |

| Integrated<br>ARM Cortex-A9<br>MPCore Processor<br>System | SE Variant                                                                                                             | SX Variant                                                                                             | ST Variant                                                                              |

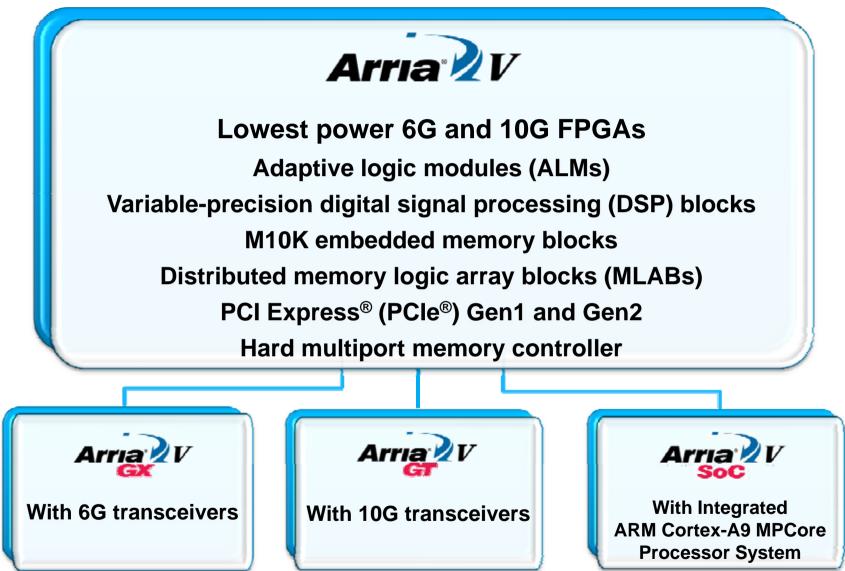

## **Arria V FPGAs**

©42012 Altera Corporation Public

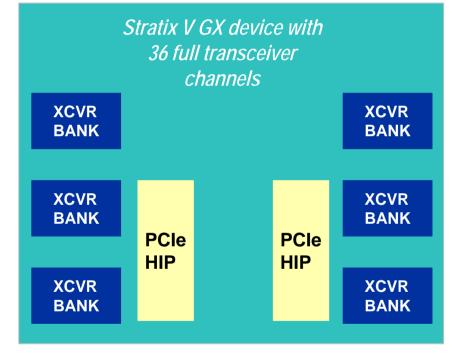

# **Stratix V Device Family Variants**

### Stratix V E variant

For highest density, high-performance applications

### Stratix V GS variant

Optimized for high-performance, high-precision DSP applications with transceivers up to 14.1 Gbps

### Stratix V GX variant

Up to 66 transceivers at 14.1 Gbps for high performance, high bandwidth

## Stratix V GT variant

28 Gbps for high-performance, ultra-high bandwidth applications

28-Gbps Transceivers

Variable-Precision DSP Block

# **Transceiver Locations**

# **Transceiver Layout**

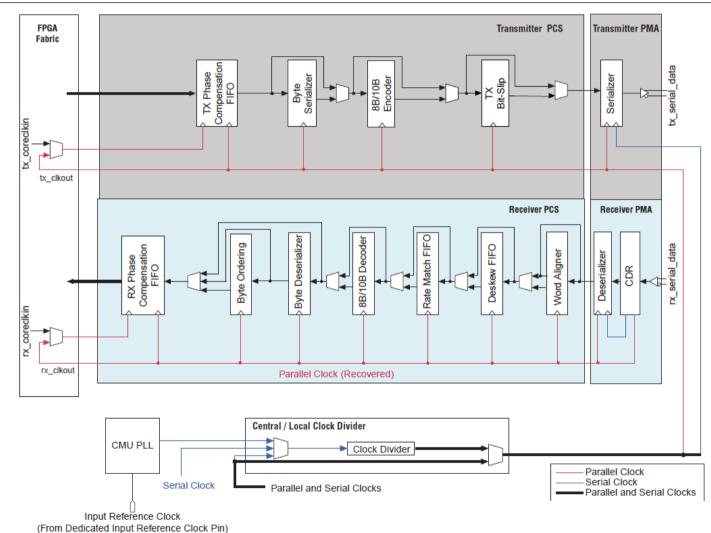

# **Standard PCS Datapath**

#### Figure 1–18. Standard PCS Datapath in Stratix V GX Channels

© 2012 Altera Corporation Public

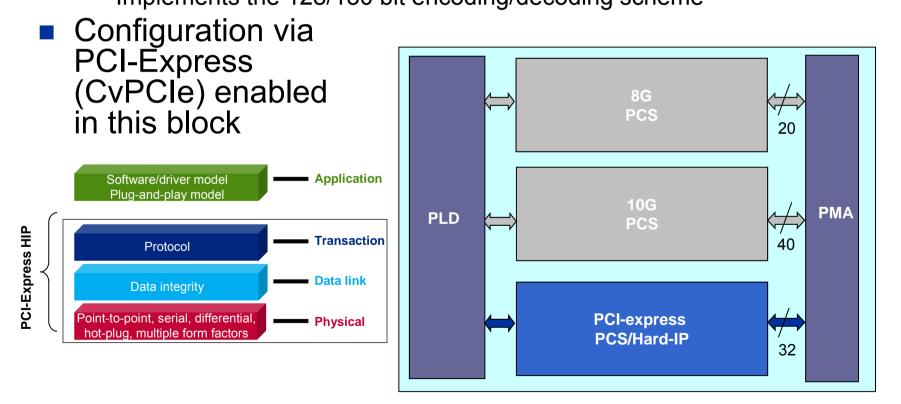

# **PCI-Express Hard-IP**

- Stratix V PCIe Gen 3/2/1 x8 HIP with 256 bit architecture

- New Stratix V PCIe Gen3 32-bit PCS used with HIP

Implements the 128/130 bit encoding/decoding scheme

© 2012 Altera Corporation—Public

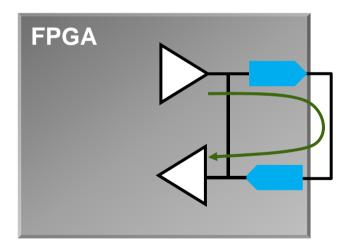

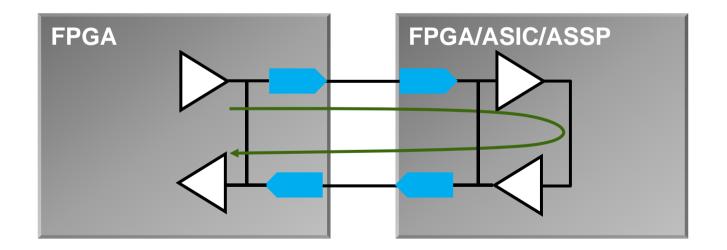

# HSIO Link Architecture Advancement Path

Time

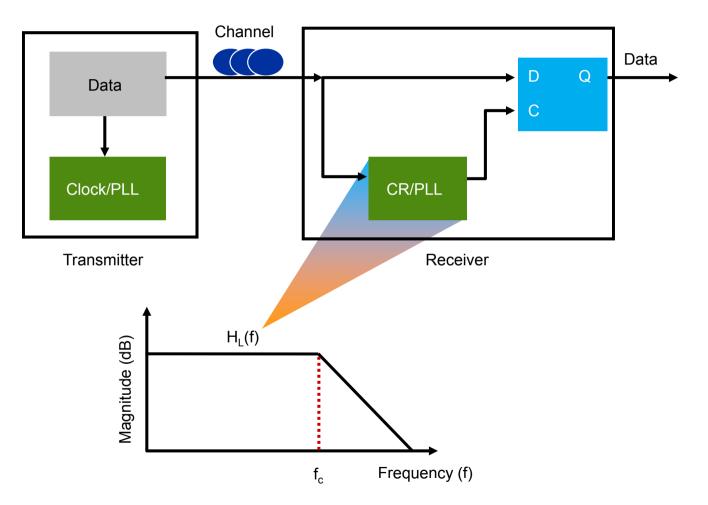

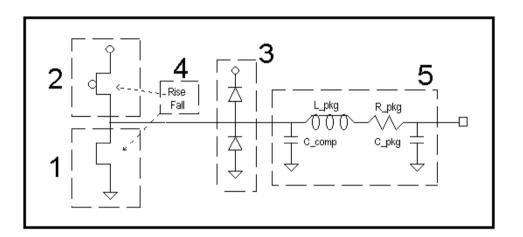

# Serial Data Communication System Using a Transceiver

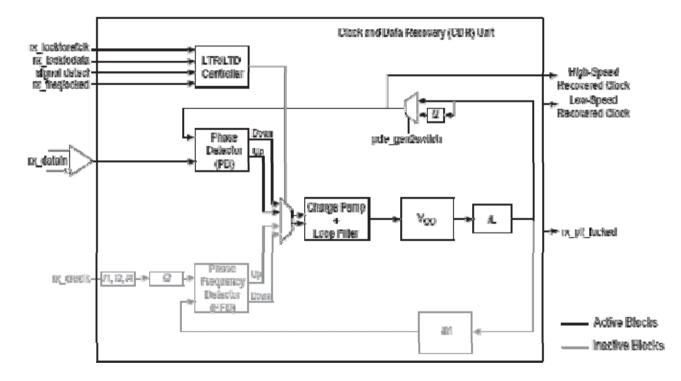

# **Clock and Data Recovery (CDR)**

- CDR has lock-to-clock and lock-to-data modes

- CDR is first locked to the reference clock, then switched to lock the data, providing fast locking time

- No unlocked or out-of-lock problems when the received data has excessive jitter

- Reference clock jitter does not affect CDR jitter performance

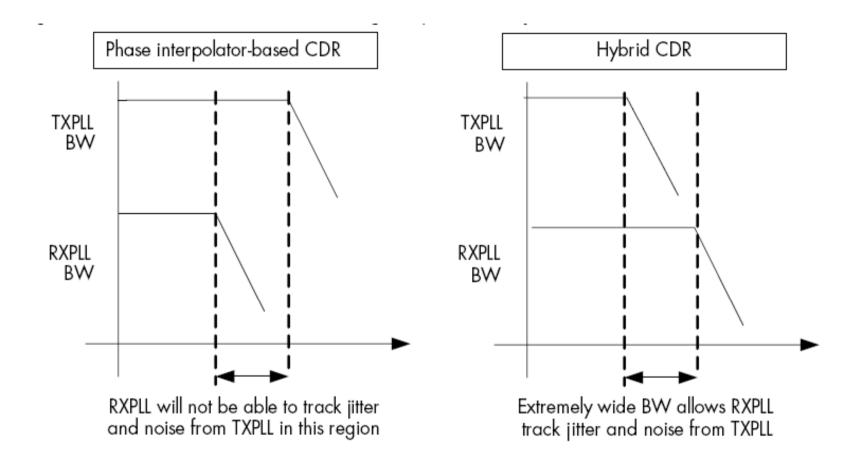

# The importance of a high bandwidth

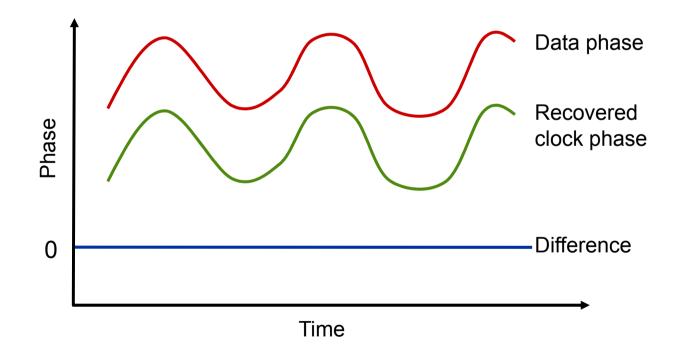

# **Jitter and Reference Clock**

- What matters in a link system is the relative jitter referenced to the recovered clock

- The net jitter is the phase difference between the data and the recovered clock

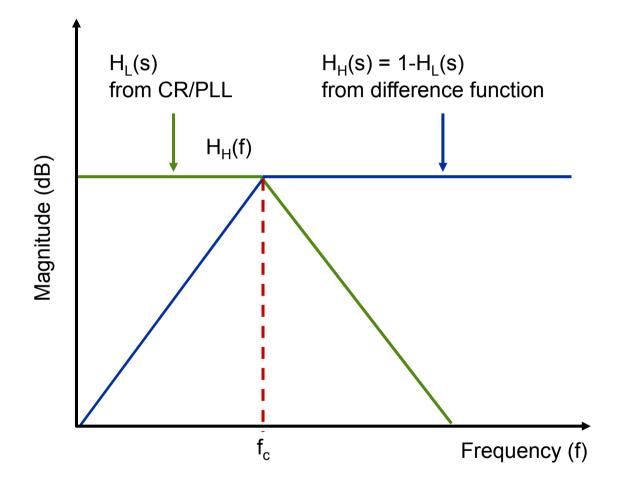

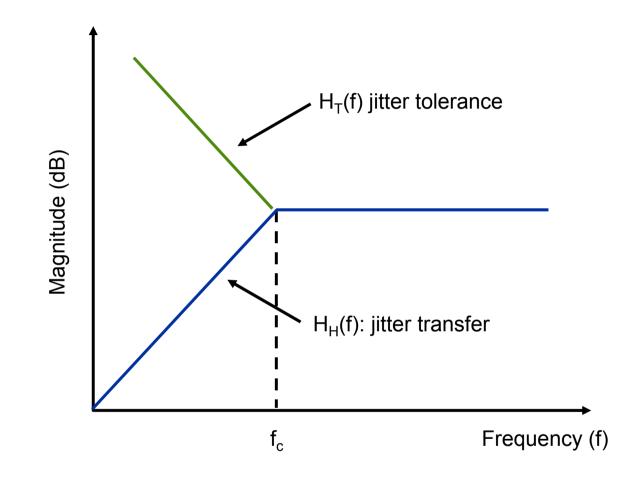

# **Jitter Transfer Function**

# **Jitter Tolerance Function**

■ Higher f<sub>c</sub>, better jitter tracking, better jitter tolerance

© 2012 Altera Corporation Public

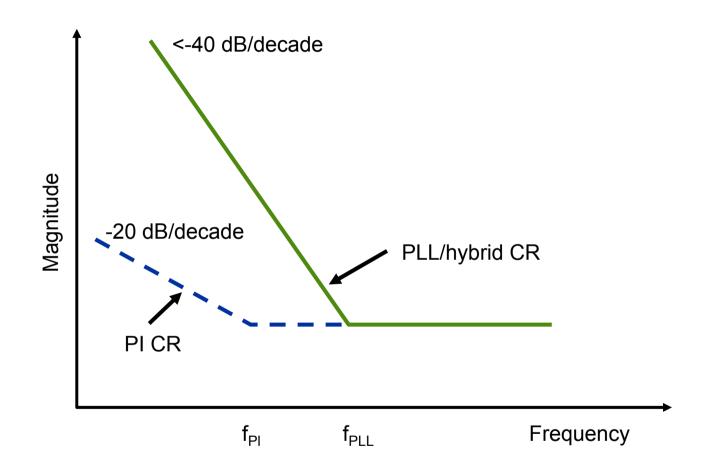

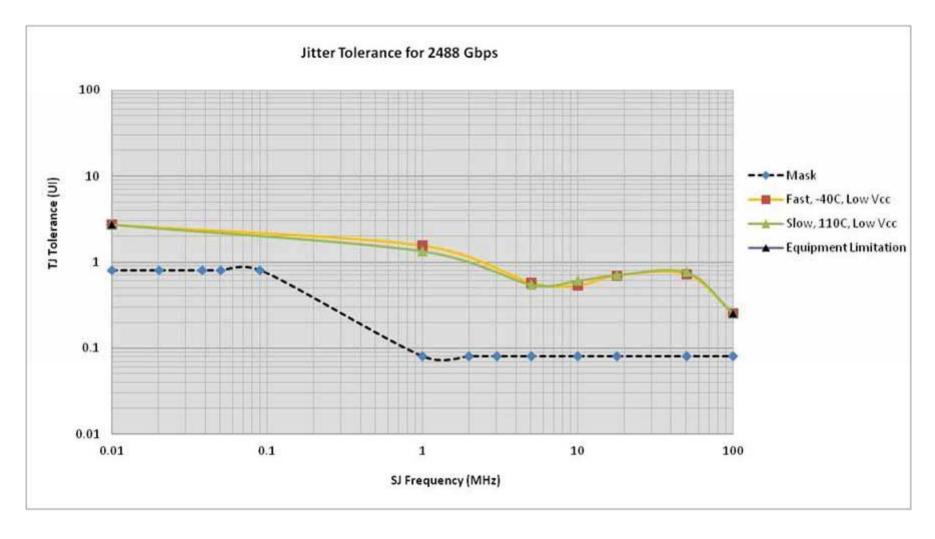

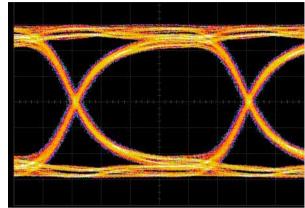

# **Jitter Tolerance Comparison**

Receivers have a hybrid phase-locked loop (PLL)-based CDR technology that has the best jitter generation and jitter tolerance performance

# The proof !

## **Transmitter PLL**

© 2012 Altera Corporation—Public

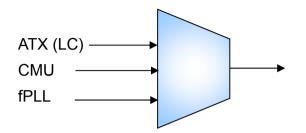

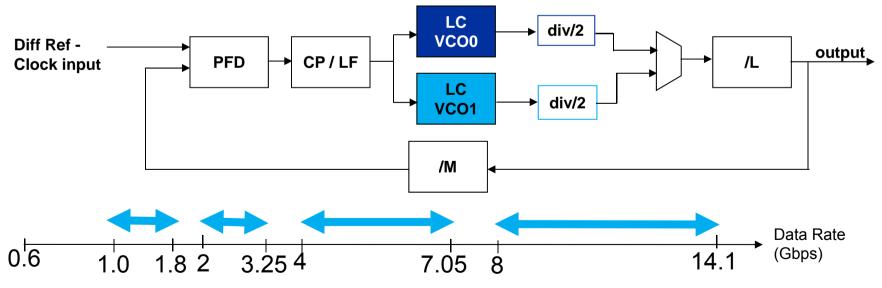

# **Transmit Clocking Options**

- Clocking options enabling independent data rates and flexible clock distribution network

- ATX PLL (LC)

- Wider operating range enabled by different VCO modes

- Sub-picoseconds of jitter for high statistical reliability

- Clock Management Unit (CMU)

- Ring Oscillator for continuous operating range with best in class jitter

- fPLLs can be used for transceivers in addition to general device clocking

| Transmit PLL option      | Data Range<br>(Gbps) | Benefit                 |

|--------------------------|----------------------|-------------------------|

| ATX (LC) PLL             | 1 – 14.1             | Best jitter performance |

| CMU (Ring<br>Oscillator) | 0.6 – 12.5           | Best data-rate range    |

| fPLL                     | 0.6 – 3.75           | Additional PLL source   |

# Up to 44 independent 12.5Gbps channels on a single Stratix V FPGA

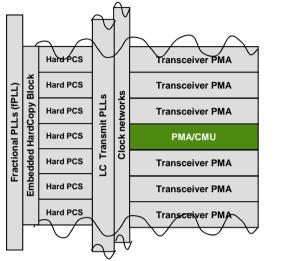

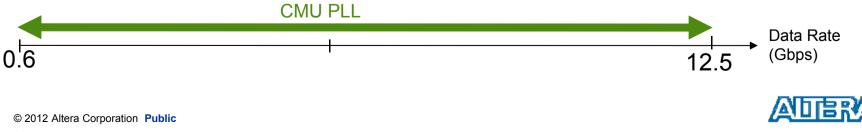

# **CMU PLL Operating Range**

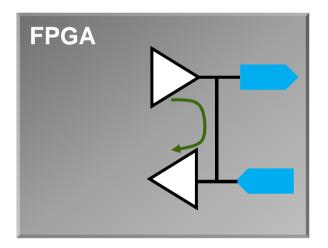

- Each channel can be configured as data channel or as CMU (clock management for the transmit PLL)

- Similar CMU to Stratix IV Ring-oscillator

- Wide operating range with low transmit jitter

- 0.6Gbps – 12.5Gbps

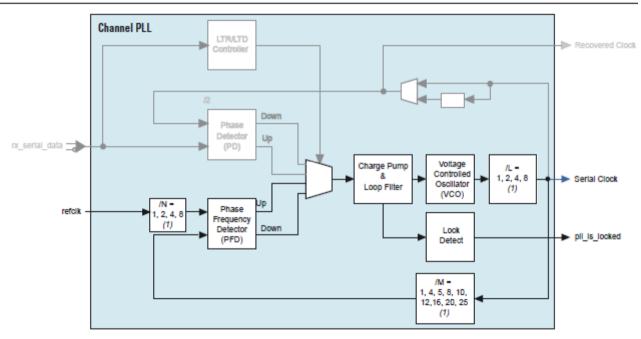

# **CMU PLL**

#### If you use Channel PLL as CMU PLL the RX is unavailable (no CDR)

#### Figure 1-10. Channel PLL Configured as CMU PLL in Stratix V Devices

#### Note to Figure 1–10:

(1) Not all combinations of /N, /M, and/L values are valid. The Quartus II software automatically chooses the optimal values.

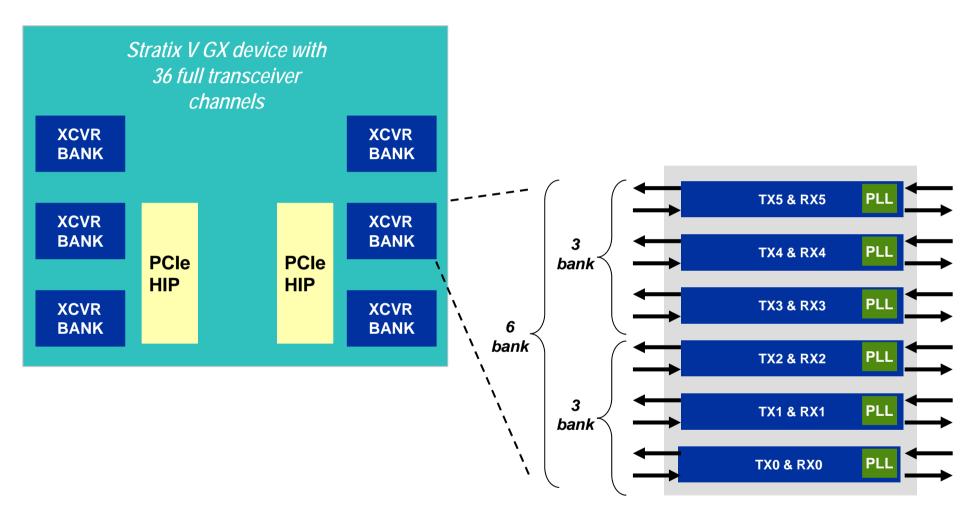

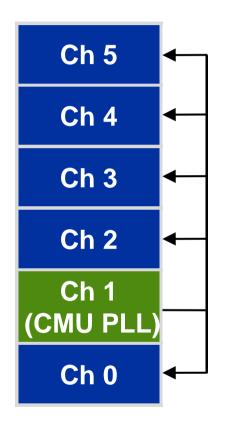

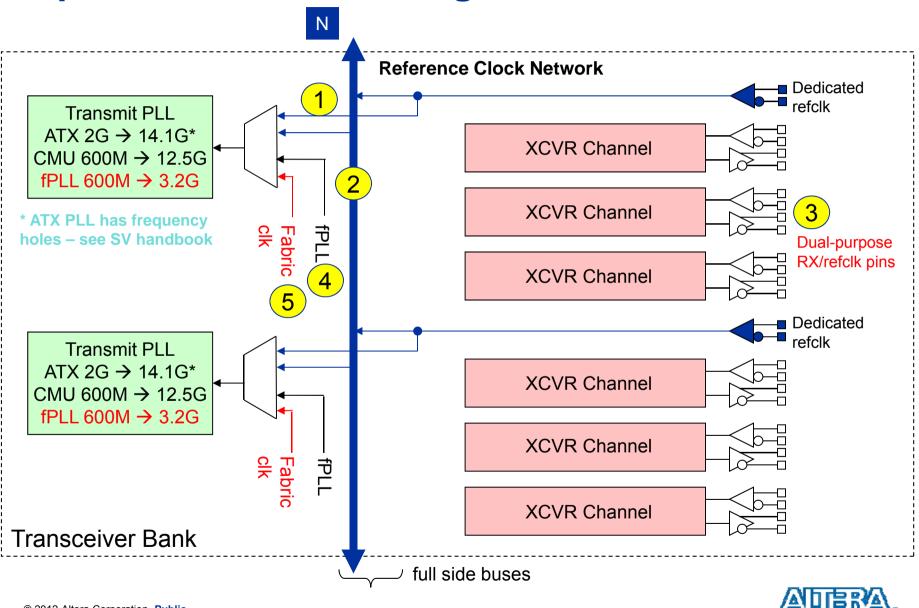

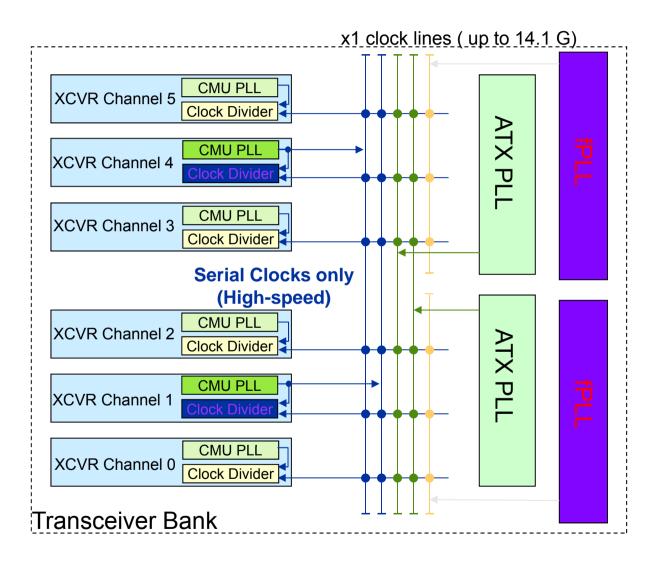

# **CMU PLLs**

- CMU PLLs in channels 1 and 4 in 6 transceiver bank can generate clocks for other transceiver channels within or outside transceiver bank

- CMU PLL channel may still be used as TX-only channel

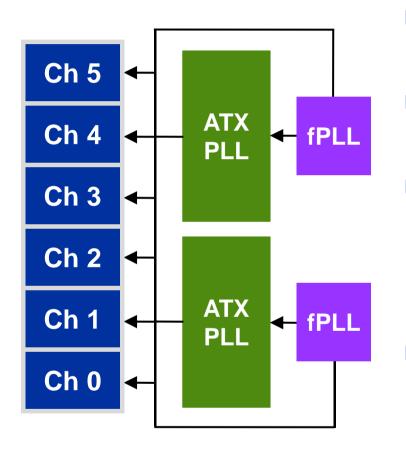

# **Programmable ATX PLL**

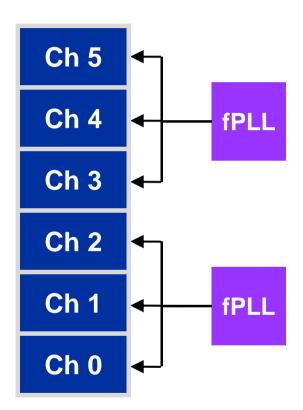

- 1 ATX PLL / 3 channels (triplet)

- Sub-picoseconds jitter achieved with LC PLL

- Programmable ATX (LC) PLL Range

- 8 Gbps 14.1 Gbps

- 4 Gbps 7.05 Gbps

- 2 Gbps 3.525 Gbps

- 1 Gbps 1.7625 Gbps (using local divider)

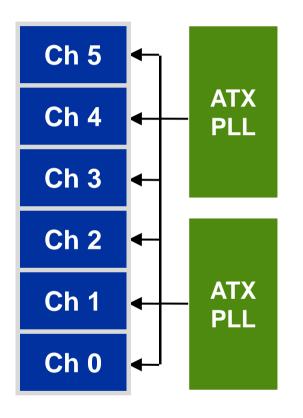

# **Stratix V ATX PLLs**

- Better jitter performance at higher data rates than CMU PLLs

- Limited frequency support

- Must be tuned to support a target data range

- Two per 6-transceiver bank

- Allow full use of device transceiver channels

- Channel PLL can be used as CDR PLL

- Stratix V GT (28G) channels must use ATX PLLs

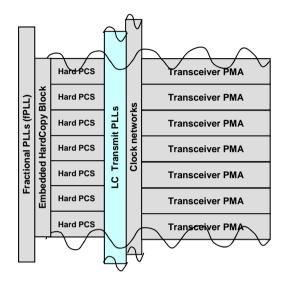

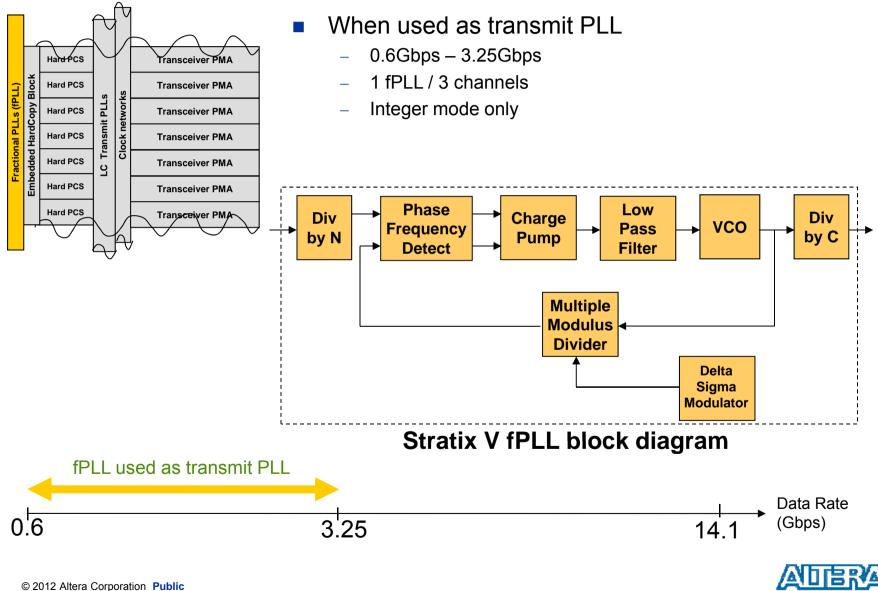

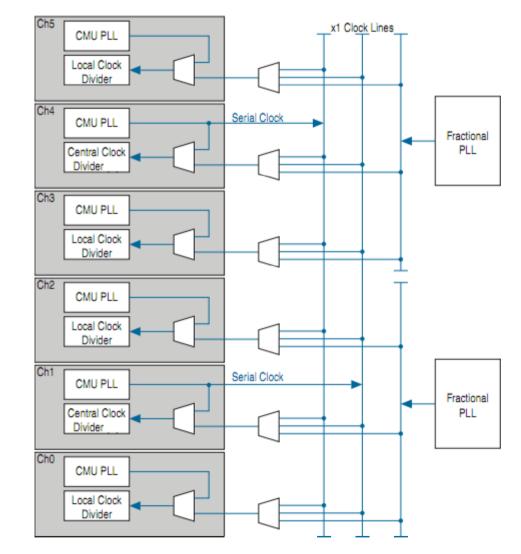

# **Fractional PLL (fPLL)**

# **Fractional PLLs**

- Can serve directly as transmitter PLL

- Data rate dependant

- Provide increased multiplication/division factors over CMU PLLs

- Allows full use of device transceiver channels

- Channel PLL can be used as CDR PLL

## **Other use of Fractional PLLs**

- Supported in Stratix V and Arria V

- Generate reference clock for channel/ATX PLLs

- Provide increased multiplication/division factors

- Support using a reference clock frequency not directly supported by channel/ATX PLLs

- Drive reference clock lines that span the sides of FPGA

- Can be segmented per transceiver bank

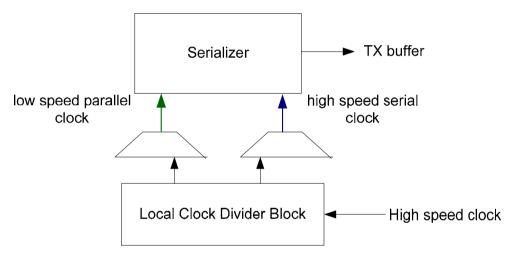

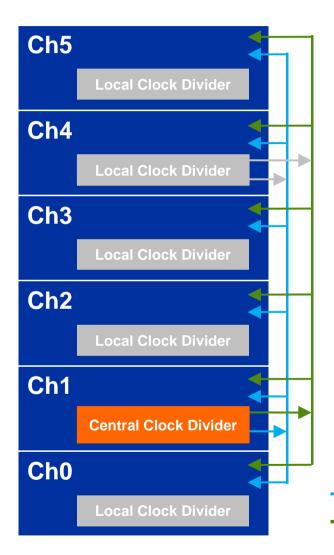

# **Transmitter Local Clock Dividers**

- One in each channel

- Receive high speed serial clocks from any transmitter PLL

#### Generates

- High-speed serial clock for local PMA

- Low-speed parallel clock for local PMA/PCS

- Active in non-bonded (x1) mode

- Each channel divides highspeed clock to support its individual target data rate

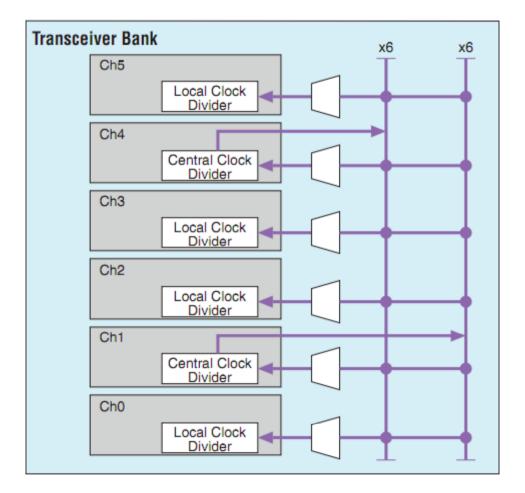

# **Central Clock Dividers**

- Special functionality of local clock dividers in channels 1 and 4 of transceiver bank

- Each central clock divider can generate high-speed serial AND low-speed parallel clocks for *bonded* channels

- High-speed serial clockLow-speed parallel clock

### **Transceiver PHY IP Cores**

- Set of IP Cores that enable/configure the FPGAs PCS/PMA layers for high-speed designs

- Both protocol-specific and generic cores available

- Implementation

- Embedded transceivers

- Core logic

- Both

## **Protocol-Specific PHY IP Cores**

- 10GBASE-R

- 10GBASE-KR

- XAUI

- Interlaken

- PHY IP core for PCI Express

- Hard IP for PCI Express

...

### **Non-Protocol-Specific PHY IP Cores**

- Custom

- Low Latency

- Deterministic

- Native PHY

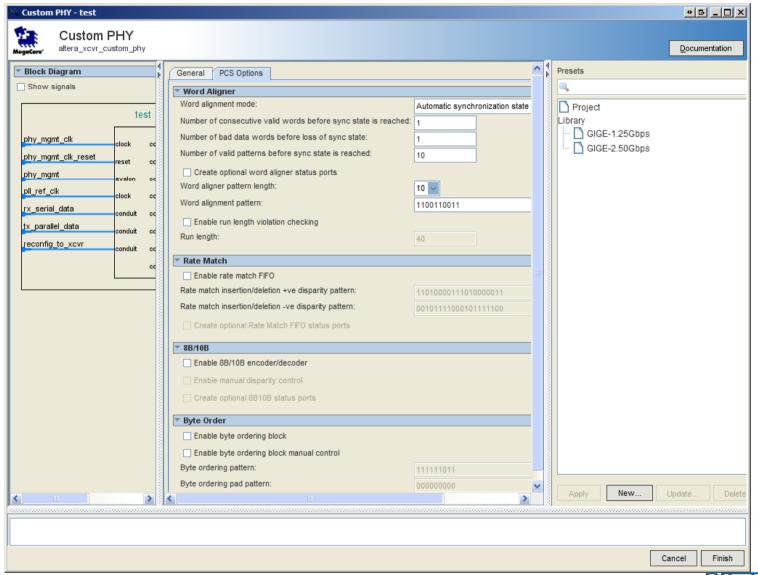

# **Custom PHY IP**

#### Overview

- Provides all PCS blocks

- Available only for the Standard PCS

- Alway includes Phase Compensation Fifo

#### Generic PHY for supporting custom interfaces

- Proprietary protocol

- No protocol-specific PHY IP available

Excellent for custom / proprietary protocols!

# **Custom PHY IP Parameter Editor (1)**

| Eustem PHY<br>altera_xcvr_custom_phy         Block Diagram         Show signals         Image: state sta | Ceneral       PCS Options         Options       Presets         Device family:       Cyclone V         Parameter validation rules:       Custom         Mode of operation:       Duplex         Number of lanes:       1         Enable lane bonding       FPGA fabric transceiver interface width:         PCS-PMA Interface Width:       Imput clock frequency:         PLL type:       CMU         Input clock frequency:       75.0 MHz         Input clock frequency:       75.0 MHz         Create tx_coreclkin port       Create optional ports         Avaion data interfaces       Imput clock frequency: |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Apply New Update Delete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# **Custom PHY IP Parameter Editor (2)**

© 2012 Altera Corporation Public

## Low Latency PHY IP Core

- Generic PHY for implementing low latency configurations in Stratix V transceivers

- Protocols/interfaces where specific PCS functionality not available and/or designer wants lowest datapath latency

- PCS functionality must be implemented in the FPGA core

- Contains

- PMA and minimal (or no) PCS

- PMA and PCS register map

- Reset controller (optional)

- PHY management interface

- Supported devices, PCS configurations and data rates

- Stratix V Low-Latency PCS: 1 14.1 Gbps

- All protocol-specific blocks bypassed

- Stratix V GT PMA Direct: 20 28 Gbps

# Low Latency PHY IP

#### Overview

- Provides a simple and a low latency path through the PCS

- Both the Standard and 10G PCS available

Excellent for custom / proprietary protocols!

# Low Latency PHY IP Parameter Editor

| Block Diagram     Show signals      Iow_latency_phy     phy_mgmt_clk     clock conduit     tx_ready,     phy_mgmt_clk_reset     reset conduit     phy_mgmt     avalon conduit     pll_locked     pll_ref_clk     clock conduit     rx_is_lockedtoref     tx_parallel_data     conduit conduit     rx_is_lockedtodata     rx_clkout     conduit     conduit     rx_clkout     conduit     rx_parallel_data     conduit     rx_clkout     conduit     rx_oready,     reconfig_to_xcvr     conduit     conduit     rx_oready,     reconfig_from_xcvr     attera_xcvr_low_latency_phy | General       Additional Options       Reconfiguration       Analog Options         Device family:       Stratix V         Data path type:       10G       Image: Comparison of the strate |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Info: Iow_latency_phy: PHY IP will require 2 reconfiguration interfaces for connection to the external reconfiguration controller.<br>Info: Iow_latency_phy: Reconfiguration interface offset 0 is connected to the transceiver channel .<br>Info: Iow_latency_phy: Reconfiguration interface offset 1 is connected to the transmit PLL .                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

© 2012 Altera Corporation Public

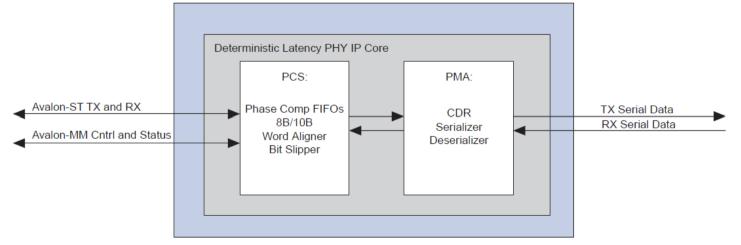

# **Deterministic PHY**

- Overview

- known timing for the transmit (TX) and receive (RX) datapaths

- Phase comp fifo in register mode

- Supports

- Auto-Rate Configuration

- User initiated via Reconfiguration Controller

- Support all CPRI/OBSAI data rates in 8G Hard PCS

- CPRI 614.4Mbps to 9.8304Gbps

- OBSAI 768Mbps to 6.144Gbps

### **Deterministic PHY IP Parameter Editor**

| Block Diagram         Show signals         bhy_mgmt_clk         bhy_mgmt_clk_reset         reset       conduit         phy_mgmt       avalon         phy_mgmt       avalon         pll_ref_clk       clock         conduit       rx_bitslipboundaryselectout         tx_parallel_data       conduit         conduit       conduit         tx_datak       conduit         reconfig_to_xcvr       conduit         conduit       conduit         rx_datak       rx_datak         rx_conduit       rx_datak         rx_conduit       conduit         rx_datak       reconfig_from_xcvr         altera_xcvr_det_latency       altera_xcvr_det_latency | General       Additional Options       Reconfiguration         Device family:       Stratix V         Mode of operation:       Duplex •         Number of lanes:       1         FPGA fabric transceiver interface width:       32 •         PCS-PMA interface width:       20 •         PLL type:       CMU •         Data rate:       4914.2 Mbps         Base data rate:       4914.2 Mbps •         Input clock frequency:       122.855 MHz •         Call Enable tx_clkout feedback path for TX PLL | Presets |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| <ul> <li>Info: det_lat_phy: PHY IP will require 2 reconfiguration interfaces for connection</li> <li>Info: det_lat_phy: Reconfiguration interface offset 0 is connected to the transcei</li> <li>Info: det_lat_phy: Reconfiguration interface offset 1 is connected to the transmit</li> </ul>                                                                                                                                                                                                                                                                                                                                                   | to the external reconfiguration controller.<br>ver channel .                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

© 2012 Altera Corporation Public

# Custom/Low Latency/Deterministic PHY IP Block Diagram

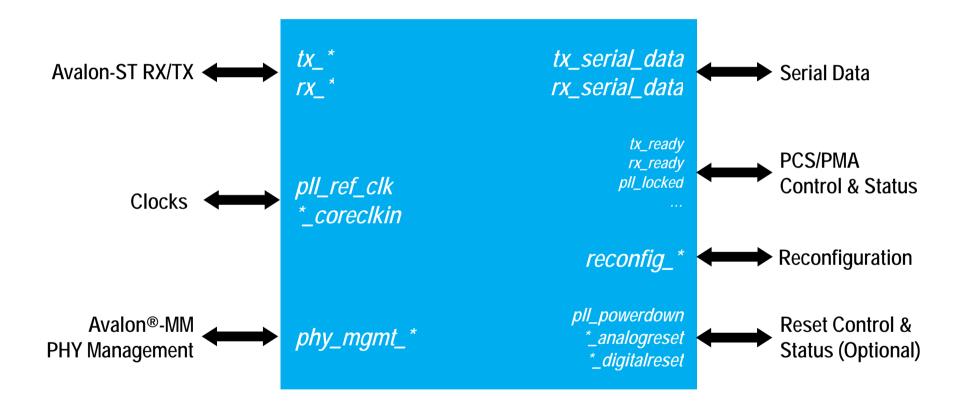

# Custom/Low Latency/Deterministic PHY IP Interfaces

- Clock interfaces

- To reference clock sources

- To MAC

- To any additional PCS blocks implemented in FPGA (as needed)

- Avalon-ST TX/RX interfaces to MAC or user logic

- Serial data interface to external channel

- Avalon-MM PHY management interface to MAC or PCS/PMA control logic

- Transceiver reconfiguration interface to reconfiguration controller

- Reset control and status reset control logic

- PCS/PMA control and status (optional) to MAC or PHY control logic

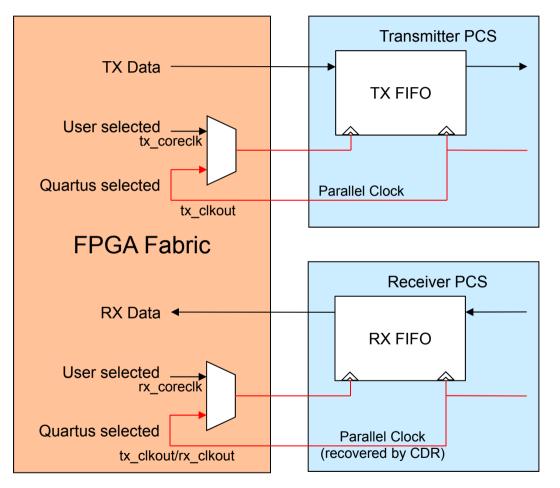

### **Clock Interfaces**

- pll\_ref\_clk: Input reference clock(s)

- tx\_clkout: Output clock from PHY to use for synchronizing TX output data, control and status signals

- rx\_clkout: Output clock from PHY; synchronized to RX data, control and status signals

- tx\_coreclkin: Optional write-side transmitter phase compensation FIFO input clock

- rx\_coreclkin: Optional read-side receiver phase compensation FIFO input clock

# **Avalon-ST Input/Ouput Interfaces**

- Connects MAC to Custom PHY IP core

- Implements simple Avalon-ST interface with no backpressure or latency

- Interface is always ready to send/receive data

- Logic must be ready to send/receive as soon as reset is complete

- Transmit signals

- tx\_parallel\_data: Outgoing input data to PHY

- Receive signals

- rx\_parallel\_data: Incoming output data from PHY

\* For more information on the Avalon specification, please see the <u>Avalon Interface Specification</u>.

### **Serial Interface**

- Connects transmitter data output(s) and receiver data input(s) to external serial interface

- Backplane

- Physical medium dependent (PMD) interface

- Another FPGA

#### Signals

- *tx\_serial\_data*: Transmitter data output

- *rx\_serial\_data*: Receiver data input

## **PHY Management Interface**

- Provides a memory-mapped register space used to access

- PCS/PMA control and status registers

- Reset control registers

- Transceiver reconfiguration registers

#### Avalon-MM standard interface

- 32-bit data, 9-bit address

- Use read/write transactions to access register space

#### Example control/status registers

- PLL locked status

- Reset RX/TX channel

- Bit/byte reversal

- Manual Wordalignment

- FIFO overflow/underflow

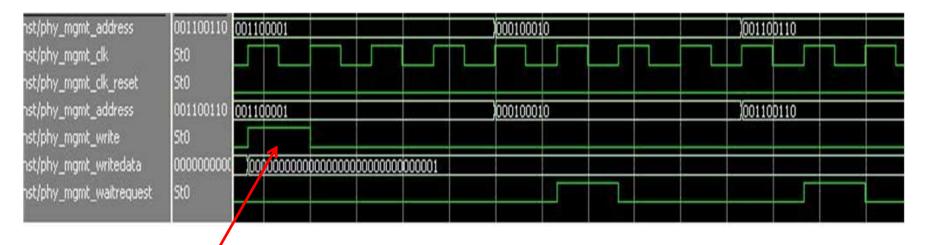

# PHY Management Avalon Write Transaction

phy\_mgmt\_write should be asserted for one clock cycle, because phy\_mgmt\_waitrequest is de-asserted

- At rising edge of phy\_mgmt\_clk, provide phy\_mgmt\_ address[8:0], phy\_mgmt\_writedata[31:0] and assert phy\_mgmt\_write

- Hold these values until PHY IP de-asserts phy\_mgmt\_waitrequest

- PHY IP captures phy\_mgmt\_writedata[31:0], de-asserts phy\_mgmt\_waitrequest and ends the transfer

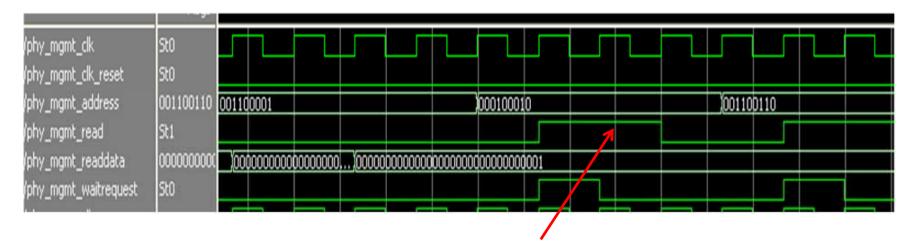

# **PHY Management Avalon Read Transaction**

phy mgmt read should be asserted for 2 clock cycles, because phy\_mgmt\_waitrequest is asserted

- At rising edge of *phy\_mgmt\_clk*, provide *phy\_mgmt\_address[8:0]* and assert *phy\_mgmt\_read*

- Hold these values until PHY IP de-asserts *phy\_mgmt\_waitrequest*

- PHY IP presents valid *phy\_mgmt\_readdata[31:0]* and de-asserts phy\_mgmt\_waitrequest

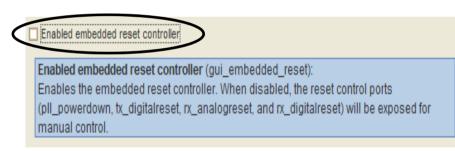

### **Reset Control & Status Interfaces**

#### Embedded reset controller enabled

- phy\_mgmt\_clk\_reset (Avalon-MM inteface): initiates reset of PHY

- *tx\_ready*: PHY has exited reset and is ready to transmit data

- *rx\_ready*: PHY has exited reset and is ready to receive data

#### Embedded reset controller disabled

- PHY provides signals to connect Transceiver PHY Reset Controller IP core or user-designed reset controller

- See device handbook for reset timing diagrams

- Examples

- pll\_powerdown : Resets TX PLL

- *tx\_cal\_busy*: Indicates transmit channel is being calibrated

- *rx\_analogreset* : Resets the RX PLL (CDR)

- *tx\_digitalreset* : Resets the TX PCS blocks

# **Optional PCS/PMA Control and Status** Interface

- Additional signals to determine and control state of PCS/PMA

- Provides instantaneous interaction over using PHY management interface

Examples

- <u>tx\_datak</u>: Input to indicate data/control code (8B/10B encoding enabled)

- *rx\_syncstatus* : Indicates single-lane word alignment

- rx\_rmfifodatainserted : Indicates Rate Match has inserted skip character

- rx\_errdetect : Indicates an 8B/10B code violation or disperity error has occurred

- *tx\_rlv*: Indicates a run length violation has occurred in the receiver

- rx\_datak: Data/control code indicator (8B/10B decoding enabled)

- <u>rx\_runningdisp</u>: Indicates disparity of incoming data (8B/10B decoding enabled)

- *rx\_enabyteordflag*: Triggers byte ordering

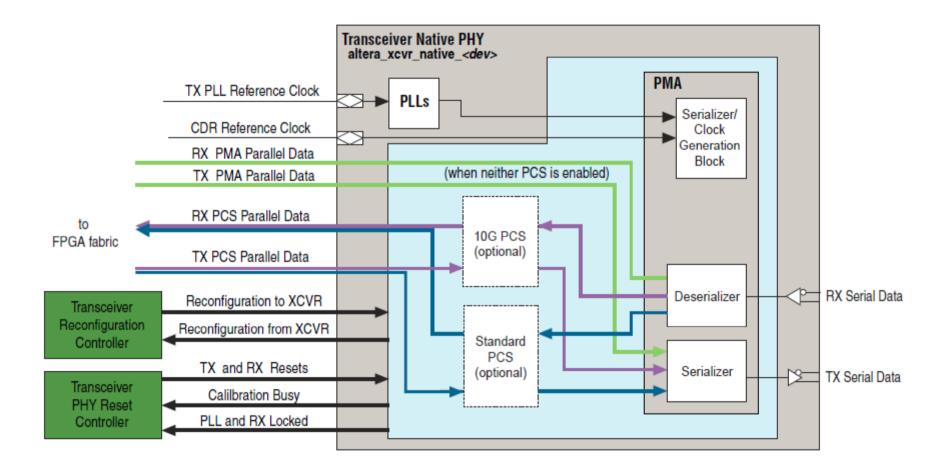

## **Native PHY**

- Give control back to the user

- First IP offering is always a family specific "Native" PHY IP.

- Lower level than PHY IP and altgx.

- Nothing but the ports and parameters. No embedded reset controller, no AVMM CSR, no fPLLs, etc.

- Protocol specific PHY IP when it makes sense.

- PIPE, Interlaken, 10GBase-KR, XAUI are good examples.

- Schedule

- 12.0 Direct Mode (only PMA)

- Reset controller as a separate optional IP

- 12.1 Full PCS Support:

- Megawizard performs validation and provides feedback for all interfaces and parameters.

- Megawizard gives warnings rather than errors when rules are violated.

# **Stratix V Native PHY**

GUI

- Parameters are grouped by functional block (8B/10B, word aligner, etc.)

- Order matches the order from the PCS diagram

#### HDL

- Parameters and ports names are intended to be self explanatory:

- Parameter naming convention:

- Standard(8G) PCS std\_rx\_<param>, std\_tx\_<param>

- 10G PCS teng\_rx\_<param>, teng\_tx\_<param>

- Port naming convention

- Standard(8G) PCS tx\_std\_..., rx\_std\_...

- 10G PCS tx\_10g\_..., rx\_10g\_...

- PMA tx\_pma\_..., rx\_pma\_...

## **Native PHY IP Cores**

#### All PHY control/status signals exposed as ports

- Similar to enabling "all optional ports" on other PHY IP cores

- No memory-mapped register interface to control and monitor PHY

- Must build own "register-space" using ports to access in memorymapped system (if required)

- Contains PHY (PCS/PMA) only

- Reconfiguration controller must be connected manually

- Reset controller must be connected manually

- Designer can use Transceiver PHY Reset Controller IP core or create own reset controller

# **Native PHY**

© 2012 Altera Corporation Public

#### **PMA GUI**

| ck Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| a         a         all powerdown       conduit       conduit       tx_pma_clkout         ix_analogreset       conduit       conduit       tx_strial_data         ix_analogreset       conduit       conduit       conduit       tx_strial_data         ix_analogreset       conduit       conduit       conduit       rx_pma_clkout         ix_analogreset       conduit       conduit       rx_pma_parallel_data         ix_analogreset       conduit       conduit       rx_ma_parallel_data         ix_analogreset       conduit       conduit       rx_s_b_lockedtoref         ix_analogreset       conduit       conduit       rx_cal_busy         ix_serial_data       conduit       conduit       conduit       tx_cal_busy         ix_ser_locktoref       conduit       conduit       conduit       reconfig_form_xcyr         ix_sist_locktoref       conduit       conduit       altera_scyr_nitive_sv         altera_scyr_nitive_sv       altera_scyr_nitive_sv       altera_scyr_nitive_sv | ✓ Parameters         ✓ Show advanced features         Number of data channels:         ▲ Enable TX data path         ✓ Enable RX data path         Selected data path:         pma_direct         Bonding mode:         non_bonded         ♥ PMA         Standard PCS         10G PCS         Data rate:         1250         PMA         Standard PCS         10G PCS         Data rate:         1250         PMA interface width:         80 ♥         TX local clock division factor:         1 ♥         TX PLL base data rate:         1250         ▼ TX PMA         ■ Enable TX PLL dynamic reconfiguration         Use external TX PLL         Number of TX PLLs:         Number of TX PLL reference clocks:         1 ♥         Main TX PLL logical index:         0 ♥         Number of TX PLL reference clocks:         1 ♥         PLL type:         CMU ♥         PL base data rate:         1250 Mbps         Reference clock frequency:         Selected reference clock source: | Mbps Mbps |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Number of CDR reference clocks:       1         Selected CDR reference clock:       0         Selected CDR reference clock frequency:       125.0 MHz         PPM detector threshold:       1000         Enable rx_pma_bitslip port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

© 2012 Altera Corporation Public

### **Standard PCS**

| how signals                                                                                                     | al                      | N                  | Parameters<br>^ Show advanced features<br>umber of data channels: 1 |

|-----------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|---------------------------------------------------------------------|

| .pll_powerdown                                                                                                  | al                      | N                  |                                                                     |

| E Contraction of the second | al                      |                    |                                                                     |

| E Contraction of the second |                         |                    | Enable TX data path                                                 |

| E Contraction of the second |                         |                    | Enable RX data path                                                 |

|                                                                                                                 | conduit conduit         |                    | elected data path: pma_direct V                                     |

| tx_digitalreset                                                                                                 | conduit conduit         |                    | onding mode: non_bonded                                             |

| tx_pll_refclk                                                                                                   | conduit conduit         |                    | MA Standard PCS 10G PCS                                             |

| tx_pma_parallel                                                                                                 |                         |                    | Enable standard PCS                                                 |

| rx_analogreset                                                                                                  |                         |                    | andard PCS protocol hint: basic V                                   |

| rx_digitalreset                                                                                                 | conduit conduit rx      | <_is_lockedtodata_ | GA fabric / Standard PCS interface width: 10 🗸                      |

| rx_cdr_refclk                                                                                                   | conduit conduit         |                    | andard PCS / PMA interface width: 10 v                              |

| rx_serial_data                                                                                                  | conduit conduit         | rx_cal_busy        | std_low_latency_bypass_enable                                       |

| rx_set_locktoda                                                                                                 | ita conduit conduit rec | config_from_xcvr   | 8B/10B                                                              |

| rx_set_locktore                                                                                                 | fconduit                |                    | Word Aligner                                                        |

| reconfig_to_xcv                                                                                                 | rr conduit              |                    | Run Length Detector                                                 |

|                                                                                                                 | alte                    | era_xcvr_native_sv | Bit Reversal/Polarity Inversion                                     |

|                                                                                                                 |                         |                    | Rate Match FIFO                                                     |

|                                                                                                                 |                         |                    | Phase Compensation FIF0                                             |

|                                                                                                                 |                         |                    | Byte Serializer/Deserializer                                        |

|                                                                                                                 |                         |                    | Byte Ordering                                                       |

|                                                                                                                 |                         |                    |                                                                     |

|                                                                                                                 |                         |                    |                                                                     |

|                                                                                                                 |                         |                    |                                                                     |

|                                                                                                                 |                         |                    |                                                                     |

|                                                                                                                 |                         |                    |                                                                     |

# **Standard PCS parameters**

|                           |                |                          | Stratix V Transs                         | eiver Native PHY - a                    | -     |

|---------------------------|----------------|--------------------------|------------------------------------------|-----------------------------------------|-------|

| Stratix V T               |                | Native PHY               |                                          |                                         |       |

| altera_xeur_hativ         | t_SV           |                          |                                          | Documen                                 | tatio |

| Diagram                   |                |                          | tid_low_latency_hypass_mable             |                                         |       |

| rsignals                  |                |                          | - 88/140                                 |                                         |       |

| [                         | a              |                          | Enable TX 8b10b encoder                  |                                         | 7     |

|                           | u.             | - I                      | Enable TX 8b10b disparity control        |                                         |       |

| pll_powerdown             | conduit condui | tx_pma_clkout            | Enable RX 8b10b decoder                  |                                         |       |

| tx_analogreset            | conduit condui | the second data          |                                          |                                         |       |

| tx_digitalreset           |                | all lacked               | Word Aligner     Enable RX word aligner: |                                         | -     |

| tx_pll_refclk             | conduit condui | av one direct            | rx_std_word_aligner_ctrl:                | bit_slip                                |       |

| tx_pma_parallel_data      | conduit condui | to any parallel data     |                                          | gige 🗸                                  |       |

|                           | conduit condui |                          | rx_std_word_aligner_sm_data_cnt:         | 3                                       |       |

| rx_analogreset            | conduit condui | 1                        | rx_std_word_aligner_sm_pattern_cnt:      | 3                                       |       |

| rx_digitalreset           | conduit condui | 1 1                      | rx_std_word_aligner_sm_err_cnt:          | 3                                       |       |

| rx_cdr_refclk             | conduit condui | rx_parallel_data         | rx_std_word_aligner_pattern:             | 00000000                                |       |

| rx_serial_data            | conduit condui | tx_std_clkout            | rx_std_word_aligner_pattern_len:         | 7 🔽                                     |       |

| rx_set_locktodata         | conduit condui | rx_std_clkout            | tx_std_bitslip_enable                    |                                         |       |

| x_set_locktoref           | conduit condui | tx_std_pcfifo_full       | 🕆 Run Length Detector                    |                                         | Ē     |

| ×_parallel_data           | conduit condui | tx_std_pcfifo_empty_     | rx_std_run_length_en                     |                                         |       |

| tx_std_coreclkin          | conduit condui | ry std pefifo full       | rx_std_run_length_val:                   | 000000                                  |       |

| rx_std_coreclkin          | conduit condui | ry std pefile empty      | The several / Polarity Inversion         |                                         |       |

| tx_std_elecidle           |                | ov std hutsonder film    | tx_std_bitrev_enable                     |                                         | 1     |

| rx_std_byteorder_ena      | conduit condui | or and hitclinhoundanced | <pre>rx_std_bitrev_enable</pre>          |                                         |       |

|                           | conduit condui |                          | tx_std_poliny_enable                     |                                         |       |

| rx_std_bitrev_ena         | conduit condui | 1 1                      |                                          |                                         |       |

| rx_std_byterev_ena        | conduit condui | 1 1                      | rx_std_polinv_enable                     |                                         |       |

| tx_std_polinv             | conduit condui |                          | Tate Match FIFO                          |                                         | 1     |

| rx_std_polinv             | conduit condui | rx_std_signaldetect      | std_rmfifo_enable                        |                                         |       |

| tx_std_bitslipboundarysel | conduit condui | tt                       | std_rmfifo_pattern1:                     | 000000000000000000000000000000000000000 |       |

| rx_std_bitslip            | conduit condui | rx_cal_busy_             | std_rmfifo_pattern2:                     | 000000000000000000000000000000000000000 |       |

| rx_std_comma_det_ena      | conduit condui | reconfig_from_xcvr       | ✓ std_coreclk_0ppm_enable                |                                         |       |

| rx_std_wa_a1a2size        | conduit        |                          | Phase Compensation FIFO                  |                                         | f     |

| rx_std_prbs_cid_en        | conduit        |                          | tx_std_pcfifo_mode:                      | low_latency                             | 1     |

| recoming to sove          | conduit        |                          | rx_std_pcfifo_mode:                      | low_latency 🖌                           |       |

|                           |                | ADMA, NYE, MENR, SY      | * Byte Serializer/Deserializer           |                                         |       |

|                           |                |                          | tx_std_byte_ser_enable                   |                                         |       |

|                           |                |                          | tx_std_byte_ser_mode:                    | div2 🔽                                  |       |

|                           |                |                          | rx_std_byte_deser_enable                 |                                         |       |

### **10G PCS – Parameter groups**

|                                                           | Stratix V Transceiver Native PHY - a |               |

|-----------------------------------------------------------|--------------------------------------|---------------|

| Stratix V Transceiver Native PHY<br>altera_xcvr_native_sv |                                      | Documentation |

| Block Diagram                                             | Show advanced features               |               |

| Show signals                                              | Number of data channels: 1           |               |

|                                                           | ☑ Enable TX data path                |               |

| a                                                         | ✓ Enable R× data path                |               |

| pll_powerdownconduittx_pma_cli                            | Selected data path: 10G 🗸            |               |

| tx_analogreset conduit conduit tx_serial_                 | Bonding mode: non_bonded 🗸           |               |

| tx_digitalreset conduit conduit pll_loc                   | PMA Standard PCS 10G PCS             |               |

| tx_pll_refclk conduit conduit rx_pma_cli                  | enable_teng                          |               |

| tx_pma_parallel_data conduit conduit rx_pma_parallel_     | teng_protocol_hint: basic            |               |

| rx_analogreset conduit conduit rx_is_lockedt              | teng_pld_pcs_width: 40 V             |               |

| rx_digitalreset conduit conduit rx_is_lockedto            | teng_pcs_pma_width: 40 🗸             |               |

| rx_cdr_refclk conduit conduit rx_parallel_                | TX FIFO                              |               |

| rx_serial_data conduit conduit tx_10g_cli                 | ► RX FIFO                            |               |

| rx_set_locktodata conduit conduit rx_10g_cli              | Frame Gen/Sync                       |               |

| rx_set_locktoref conduit conduit rx_10g_clk3;             | CRC32 Generator/Checker              |               |

| tx_parallel_data conduit conduit rx_10g_con               | ▶ 64/66                              |               |

| tx_10g_coreclkin conduit conduit tx_10g_fifo              | Scrambler                            |               |

| rx_10g_coreclkin                                          |                                      |               |

| tx_10g_control conduit conduit tx_10g_fifo_er             | Disparity Generator / Checker        |               |

| tx_10g_data_valid conduit conduit tx_10g_fifo_per         | ▶ Gearbox                            |               |

| tx_10g_diag_status conduit conduit tx_10g_fife            | Bits lip                             |               |

| rx_10g_fifo_rd_en conduit conduit tx_10g_fifo_ir          | ▶ Block Sync                         |               |

| rx_10g_fife_align_clr conduit conduit rx_10g_data_        | ▶ BER                                |               |

| rx_10g_fifo_align_enconduitrx_10g_fifo                    | F Test/Debug                         |               |

| tx_10g_bitslip conduit conduit rx_10g_fife_               |                                      |               |

| rx_10g_bitslip conduit conduit rx_10g_fife_er             |                                      |               |

| tx_10g_burst_en conduit conduit rx_10g_fifo_per           |                                      |               |

| ev 10a diea ele                                           |                                      |               |

Cancel Finish

Info: a: PHY IP will require 2 reconfiguration interfaces for connection to the external reconfiguration controller.

Info: a: Reconfiguration interface offset 0 is connected to the transceiver channel.

Info: a: Reconfiguration interface offset 1 is connected to the transmit PLL.

### **10G PCS parameters**

| ×               |                                 |         |                       | Stratix V | Transceiv      | er Native PHY       | 7 <b>8</b> 1     |        |

|-----------------|---------------------------------|---------|-----------------------|-----------|----------------|---------------------|------------------|--------|

| Stratix V Tra   | insceiver Native PHY            |         |                       |           |                |                     |                  |        |

| Stratix V Tra   |                                 |         |                       |           |                |                     |                  | Decume |

| * Block Diagram |                                 |         |                       | 10        |                |                     |                  |        |

| Show signals    |                                 |         |                       |           | teng_txfife    |                     | phase_comp w     |        |

|                 | 1                               | _       |                       |           | txmg_1xfife    | ufull:              | 31               |        |

|                 | *                               |         |                       |           | teng_txfife    |                     | 0                |        |

|                 | pll_powerdown                   | conduit | tx_pma_clkout         |           | THE STREET     |                     | 29               |        |

|                 | CONDUCT CONDUCT                 |         | tx_serial_data        |           | teng_txfifo    | _pempty:            | 7                |        |

|                 | conduct                         | conduit | pll_locked            |           | <b>RX FIFO</b> |                     |                  |        |

|                 | tx_origitaireset conduit        | conduit |                       |           | teng_rxfifo    | _mode:              | phase_comp 🔽     |        |

|                 | Condus                          | conduit | rx_pma_clkout         |           | teng_rxfifo    | p_full:             | 31               |        |

|                 | tx_pma_parallel_data conduit    | conduit | rx_pma_parallel_data  |           | teng_rxfifo    | _empty:             | 0                |        |

|                 | rx_analogreset conduit          | conduit | rx_is_lockedtoref     |           | teng_rxfifo    | o_pfull:            | 23               |        |

|                 | rx_digitalreset conduit         | conduit | rx_is_lockedtodata    |           | teng_rxfifo    |                     | 7                |        |

|                 | _rx_cdr_refclkconduit           | conduit | rx_parallel_data      |           | teng_rxfifo    | _align_enable:      | 0                |        |

|                 | rx_serial_data conduit          | conduit | tx_10g_clkout         |           | teng_rxfifo    | _control_enable:    | 0                |        |

|                 | rx_set_locktodata conduit       | conduit | rx_10g_clkout         |           | 🔻 Frame Ge     | n/Sync              |                  |        |

|                 | rx_set_locktoref                | conduit | rx_10g_clk33out       | =         | teng_t>        | <_frmgen_enable     |                  |        |

|                 | tx_parallel_data conduit        | conduit | rx_10g_control        |           | teng_tx_fr     | mgen_user_length:   | 2048             |        |

|                 |                                 | conduit | tx_10g_fifo_full      |           | teng_r:        | <_frmsync_enable    |                  |        |

|                 | rx_10g_coreclkin conduit        | conduit | tx_10g_fifo_pful      |           | teng_rx_fr     | msync_user_length:  | 2048             |        |

|                 | ty 10s control                  |         | tx_10g_fifo_empty     |           | teng_frmg      | ensync_diag_word:   | 64000000000000   |        |

|                 | conduit                         | conduit | tx_10g_fifo_pempty    |           | teng_frmg      | ensync_scrm_word:   | 28000000000000   |        |

|                 | tx_10g_diag_status              | conduit | tx_10g_fifo_del       |           | teng_frm g     | ensync_skip_word:   | lelelelelele     |        |

|                 | Condust                         | conduit |                       |           | teng_frmg      | ensync_sync_word:   | 78f678f678f678f6 |        |

|                 | rx_10g_fifo_rd_en               | conduit | tx_10g_fifo_insert    |           | teng_t>        | <_frmgen_burst_enab | ble              | -      |

|                 | rx_10g_fifo_align_clr conduit   | conduit | rx_10g_data_valid     |           | T CRC32 6      | enerator/Checker    |                  |        |

|                 | rx_10g_fifo_align_en            | conduit | rx_10g_fifo_full      |           |                | crcgen_enable       |                  |        |

|                 | tx_10g_bitslip conduit          | conduit | rx_10g_fifo_pful      |           |                | <_crcchk_enable     |                  |        |

|                 | rx_10g_bitslip conduit          | conduit | rx_10g_fifo_empty     |           |                | <_erectik_enable    |                  |        |

|                 | tx_10g_burst_en conduit         | conduit | rx_10g_fifo_pempty    |           | <b>~ 64/66</b> |                     |                  |        |

|                 | rx_10g_disp_clr conduit         | conduit | rx_10g_fifo_de        |           |                | <_64b66b_enable     |                  |        |

|                 | rx_10g_highber_clr_cnt          | conduit | rx_10g_fifo_insert    |           | teng_m         | x_64b66b_enable     |                  |        |

|                 | rx_10g_clr_errblk_count conduit | conduit | rx_10g_align_val      |           | teng_t>        | <_sh_err            |                  |        |

|                 | rx_10g_prbs_err_clr conduit     | conduit | rx_10g_blk_lock       |           | ▼ Scramble     | r                   |                  |        |

|                 | recentin to your                |         | rx_10g_blk_sh_err     |           | teng_t>        | <_scram_enable      |                  |        |

|                 | conduit                         | conduit | rx_10g_scram_err      |           | teng_m         | <_scram_enable      |                  |        |

|                 |                                 | conduit | tx_10g_frame          |           |                | n_seed_mode:        | min 🗸            |        |

|                 |                                 | conduit |                       |           | teng_scrar     | n_user_seed:        | 00000000000000   |        |

|                 |                                 | conduit | rx_10g_frame          |           | - Disparit     | Constant (Charles   |                  |        |

|                 |                                 | conduit | rx_10g_frame_lock     |           |                | Generator/Checker   |                  |        |

|                 |                                 | conduit | rx_10g_frame_mfrm_err |           |                | <_dispgen_enable    |                  |        |

|                 |                                 | conduit | rx_10g_frame_sync_err | ×         | teng_r         | <_dispchk_enable    |                  |        |

# **PHY IP Output Files for Compilation**

#### <phy\_instance\_name>.qip

- Script file that points to all files needed for synthesis

- Add file to Quartus II project

#### phy\_instance\_name>.v/.vhd

Wrapper file that instantiates and configures the PHY IP core megafunction

#### phy\_instance\_name> folder

Combination of Verilog and SystemVerilog files representing PHY IP core components

#### phy\_instance\_name>.ppf

- Stores top-level I/O and node information for importing into Pin Planner

- Useful when pin layout must be assigned before top-level file is completed

# **Additional PHY IP Cores**

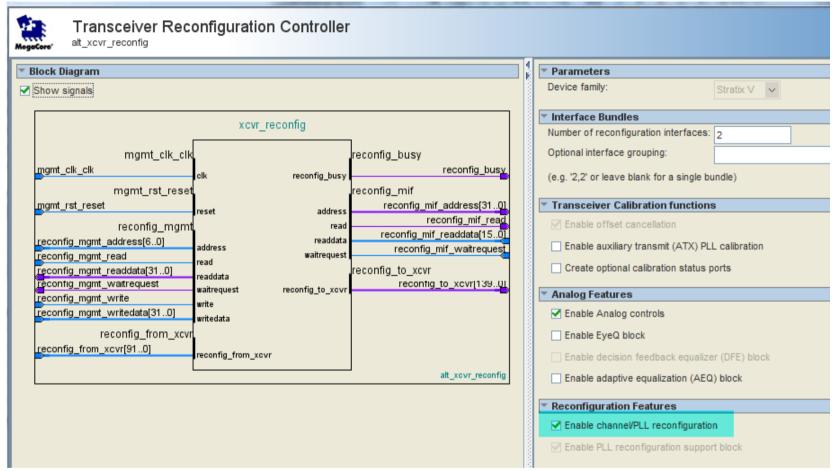

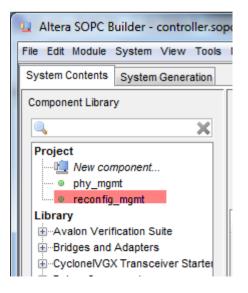

#### Transceiver Reconfiguration Controller

- Discussed later

- Transceiver PHY Reset Controller

#### **Transceiver PHY Reset Controller IP Core**

- Fully customizable reset solution

- Provides most flexible pre-built reset solution

- Enable as many or as few control/status signals as you need

- Works with all non-protocol-specific PHY IP cores

- Must disable embedded controller, if enabled by default

- Generates clear text Verilog file

- User can modify as desired

#### **Reset Controller Options**

- Shared or individual reset controls per channel in transceiver instance

- Shared or separate reset controls per each RX channel

- Shared or separate reset controls per each TX channel

- Option for manual or automatic RX/TX reset recovery when PLLs lose lock

- Configurable timing delay

#### **Reset Controller Parameter Editor**

| Block Diagram Show signals $phy_reset$ clock clo | <ul> <li>General Options         <ul> <li>Number of transceiver channels:</li> <li>Number of TX PLLs:</li> <li>Input clock frequency:</li> <li>250</li> <li>MHz</li> <li>Synchronize reset input</li> <li>Use fast reset for simulation</li> </ul> </li> <li>TX PLL         <ul> <li>Enable TX PLL reset control</li> <li>pl_powerdown duration:</li> <li>1000</li> <li>ns</li> <li>Synchronize reset input for PLL powerdown</li> </ul> </li> <li>TX Channel         <ul> <li>Use separate TX reset per channel</li> </ul> </li> </ul> | Documentation |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ose separate 1X reset per channel         TX automatic reset recovery mode:       Manual         tx_digitalreset duration:       20         pll_locked input hysteresis:       0         TX Channel       0         Tx automatic reset recovery mode:       0         Tx Channel       Image: separate RX reset per channel         RX automatic reset recovery mode:       Auto         Ix analogreset duration:       40         Ix analogreset duration:       400         Ix digitalreset duration:       4000                      | Apply         |

© 2012 Altera Corporation Public

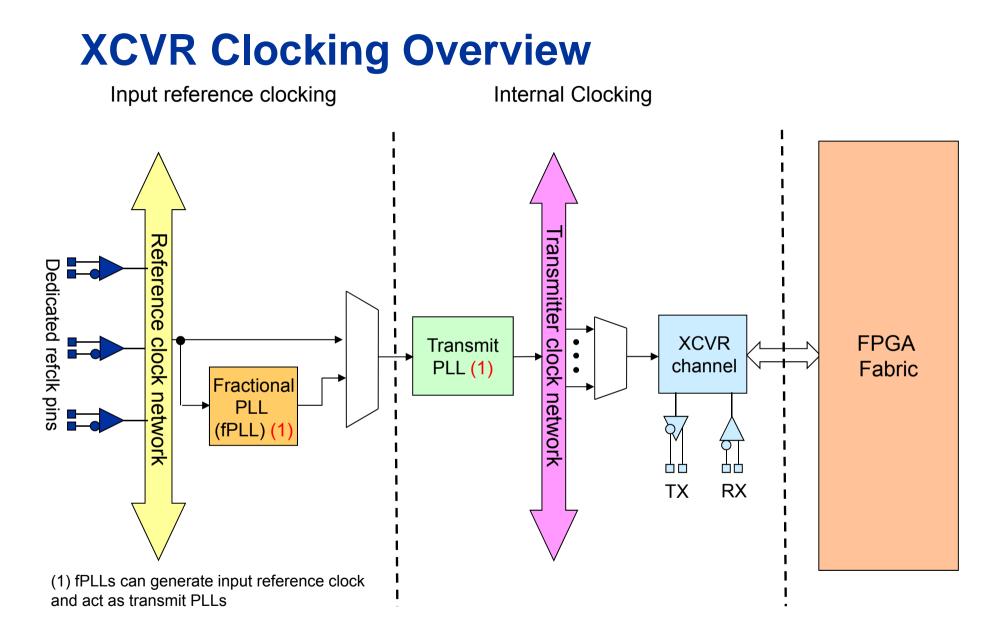

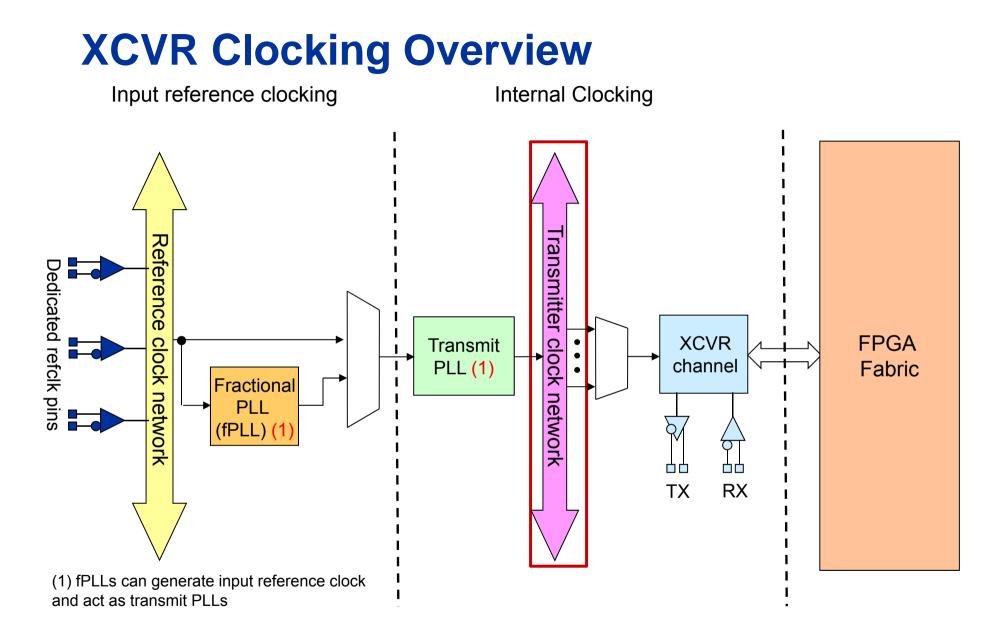

#### **Input Reference Clocking**

#### **Reference Clock Network**

- Dedicated clock routing resources spanning the sides of the FPGA

- Driven by reference clock pins

- One clock route per reference clock pin

- Exception: Arria V GT reference clock networks are segmented

- Allow reference clocks to be used by any PLL on that side of the FPGA

# **Input Reference Clocking**

#### Clock source in order of performance

- 1. Dedicated refclk pin (direct path)

- Ideally closest to the TX PLL

- 2. Dedicated refclk pin using reference clock network

- Within transceiver bank

- Outside of transceiver bank

- 3. Dual purpose RX/refclk pins

- 4. fPLL

- fPLL → TX PLL cascading can lead to high jitter

- 5. Clock from FPGA Fabric

#### **Internal Clocking: Non-bonded Configurations**

© 2012 Altera Corporation Public

# **x1 Clock Network**

- Span up to one 6transceiver bank

- Used to carry highspeed clock to transceiver channels

- Drives each channel's local clock divider

- Non-bonded operation only

- Clock source

- Ch1/Ch4 CMU PLL

- Fractional PLL

- ATX PLL

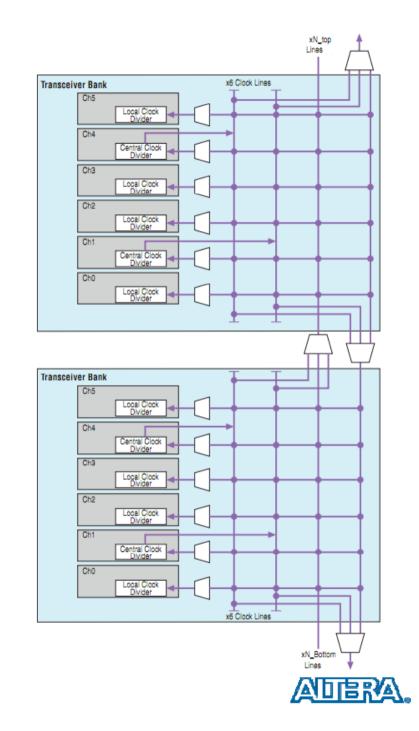

### **x6 Clock Network**

- Span up to one 6transceiver bank

- Used to carry both highspeed serial and lowspeed parallel clocks to channels within a 6transceiver bank

- Bonded operation only

- Clock source

- Central clock divider

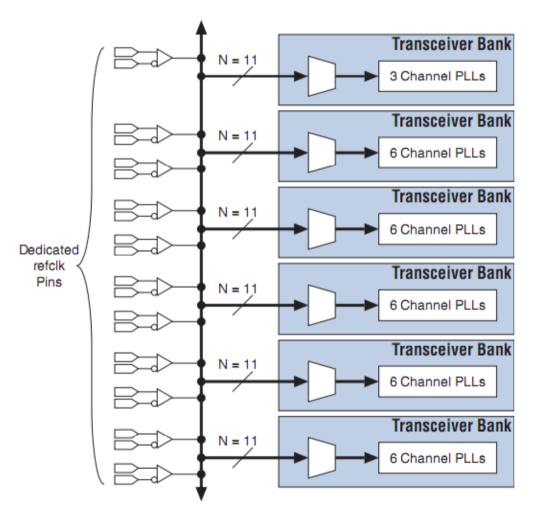

## **xN Clock Network**

- Span the entire side of the device

- Used to carry both highspeed serial and low-speed parallel clocks from x6 line to other transceiver banks

- Bonded operations only

- Clock source

- x6 clock network (from central clock divider)

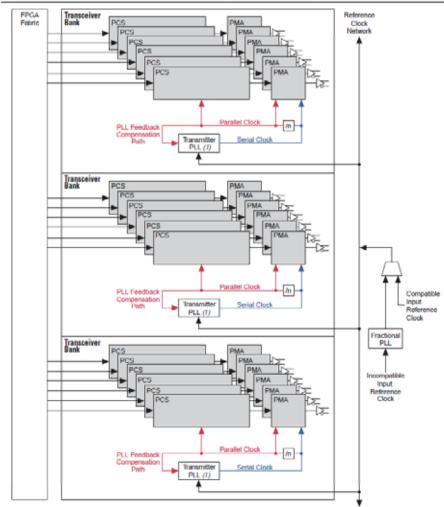

#### Internal Clocking: PLL Feedback Compensation Path Bonding

Figure 2–15. Three Transceiver Bank Channels Bonded Using the PLL Feedback Compensation Path

Note to Figure 2–15: (1) The transmitter PLL can be an ATX PLL or a GMU PLL. You can have up to six channels per bank with an ATX PLL and five channels per bank with a GMU PLL.

- For bonding channels beyond a transceiver bank with the controlled skew

- Removes divider uncertainty by aligning parallel clk with refclk

- Refclk restriction

- refclk frequency has to be the same as tx\_clkout

- fPLL can be used to match refclk and parallel clock

#### **FPGA Fabric-Transceiver Interface Clocking**

- Quartus selected option is best for:

- Bonded configurations

- User selected option is best for:

- Saving FPGA fabric clock resources for multiple identical channels

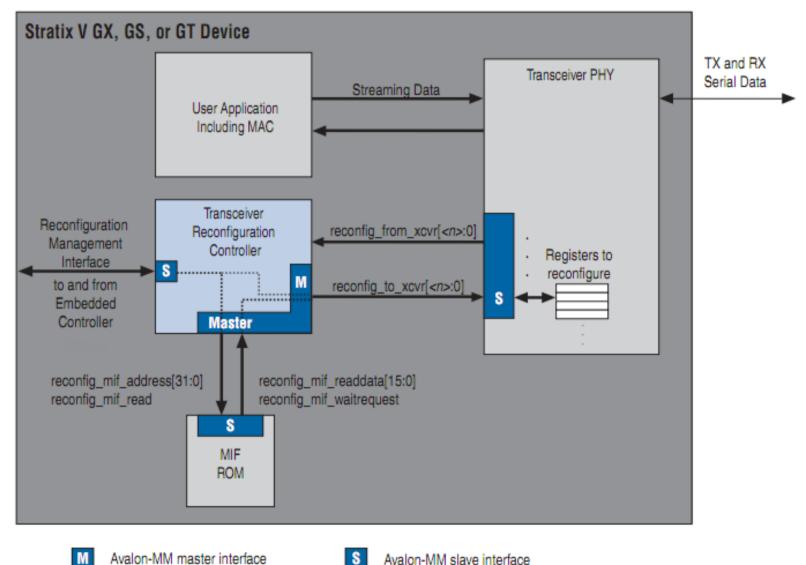

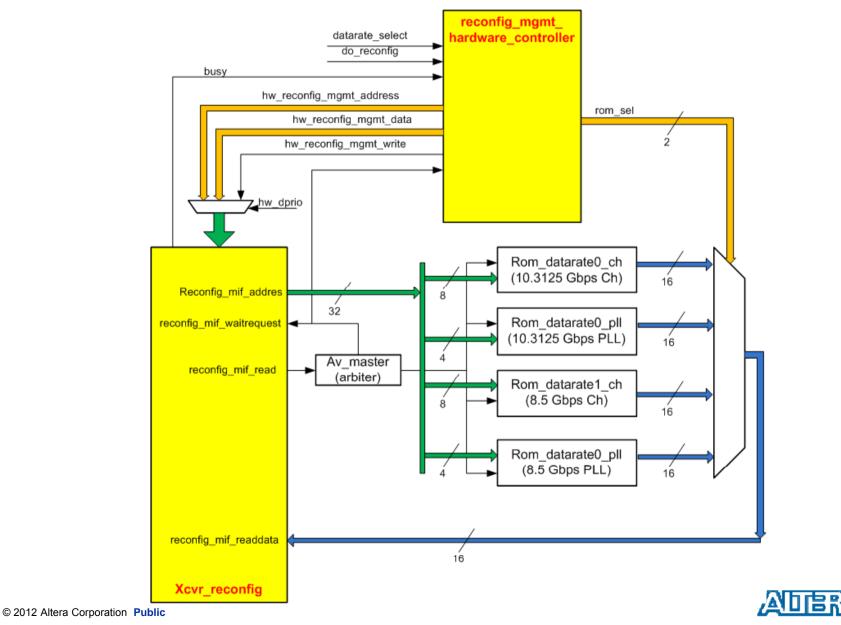

# **Transceiver Reconfiguration**

© 2012 Altera Corporation—Public

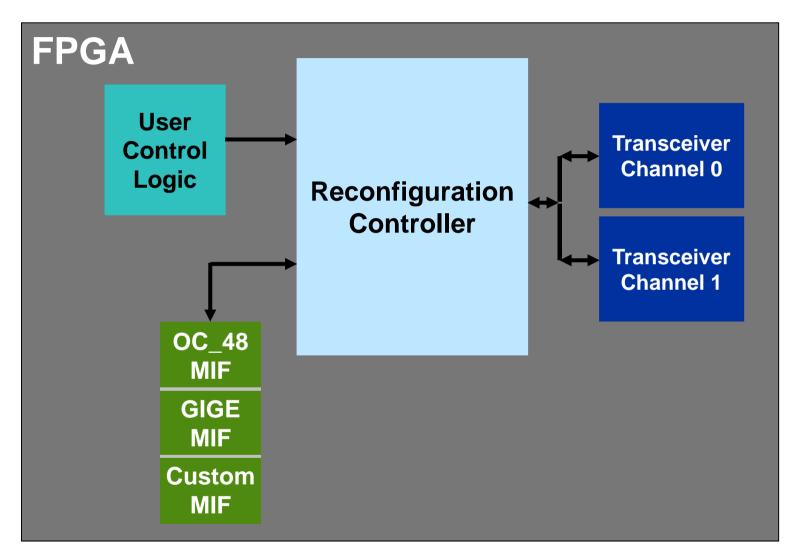

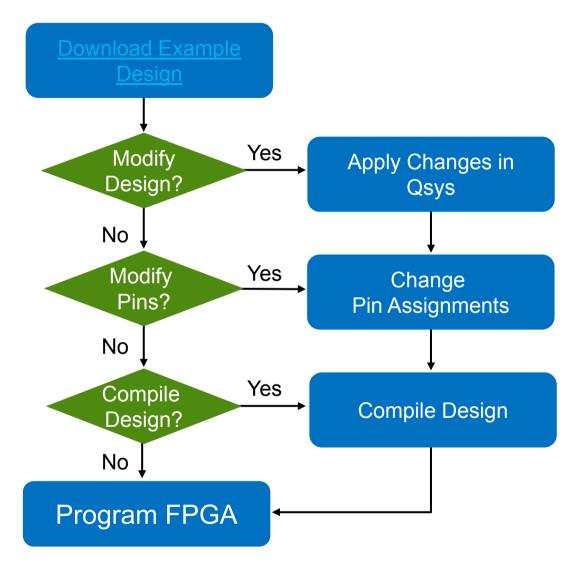

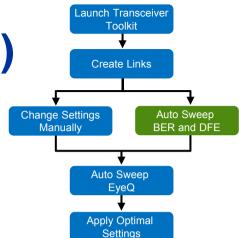

### Introduction

What is transceiver reconfiguration?

Reconfiguration of single or multiple transceiver channel settings during device operation

#### Reconfiguration of

- Physical media attachment (PMA) settings

- Physical coding sublayer (PCS) settings

- Transceiver Clocking (PLL settings)

- Run time modification does not interrupt operation of adjacent transceiver channel(s)

## **Transceiver Reconfiguration Uses**

- Adjust transmitter/receiver buffer settings while bringing up link to fine-tune signal integrity

- Increases flexibility in board/system design

- Increase/decrease data rate due to downstream/upstream device

- Support newer, changing serial protocols

- Add design flexibility by supporting multiple protocols with same hardware

# **Reconfguration and Device Support**

| Reconfiguration Feature    |                             | Device Family |              |           |  |

|----------------------------|-----------------------------|---------------|--------------|-----------|--|

|                            |                             | Stratix V     | Arria V      | Cyclone V |  |

| Calibration                |                             | ✓             | $\checkmark$ | ✓         |  |

| Analog                     | PMA Reconfiguration         | ✓             | $\checkmark$ | ✓         |  |

| Analog                     | EyeQ, AEQ, DFE              | ✓             |              |           |  |

| Loopback                   | Pre-CDR reverse serial      | ✓             | $\checkmark$ | ✓         |  |

|                            | Post-CDR reverse serial     | ✓             | $\checkmark$ | ✓         |  |

| PLL<br>Reconfiguration     | Ref Clk Switching           | ✓             | ✓*           | ✓*        |  |

|                            | TX PLL Reconfiguration      | ✓             | $\checkmark$ | ✓*        |  |

| Channel<br>Reconfiguration | RX CDR Reconfiguration      | ✓             | $\checkmark$ | ✓*        |  |

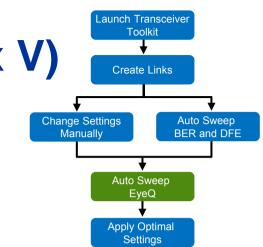

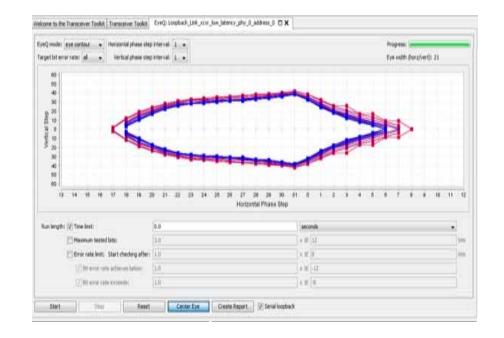

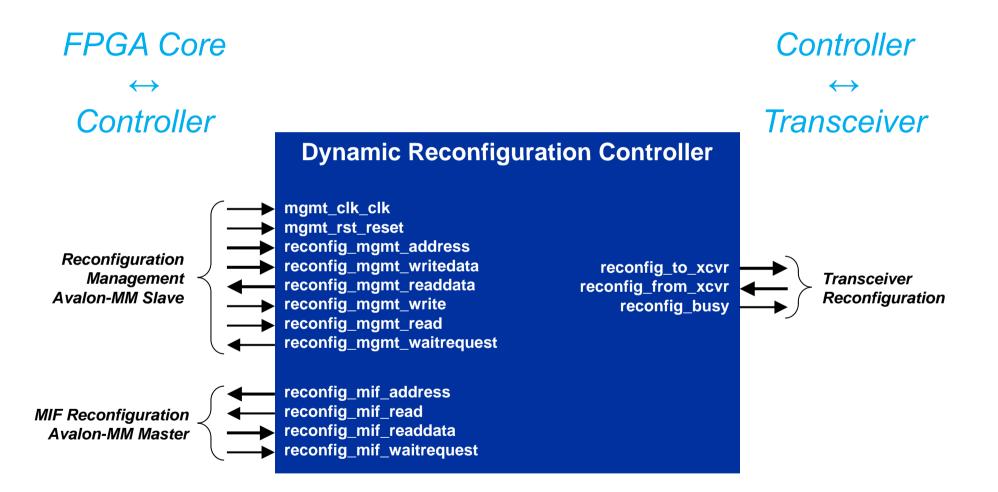

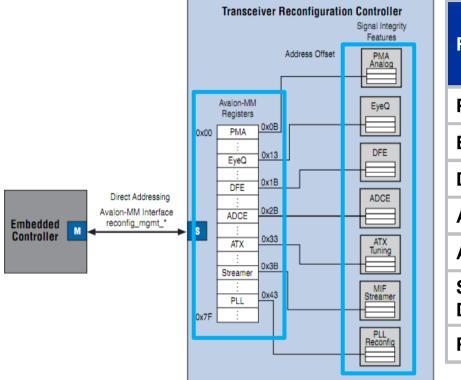

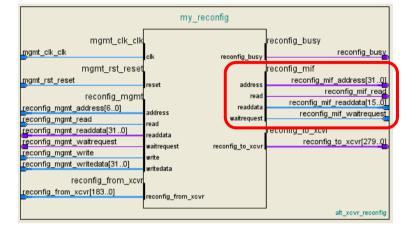

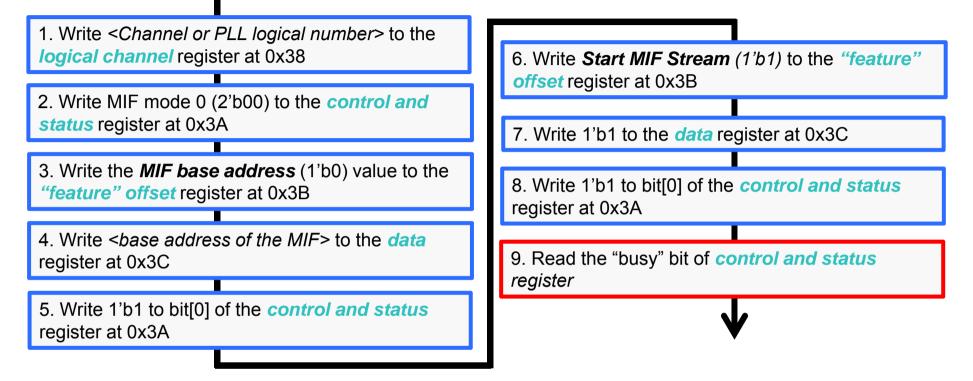

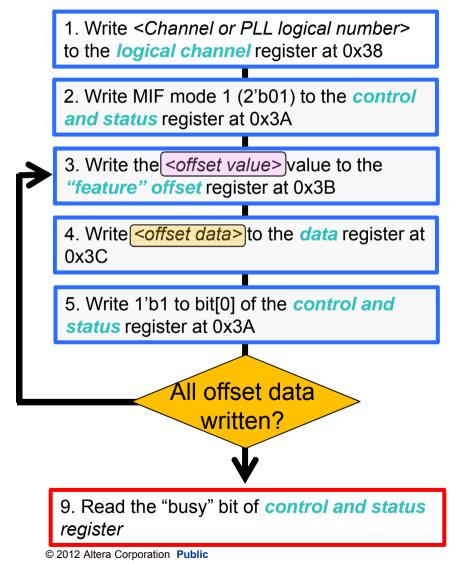

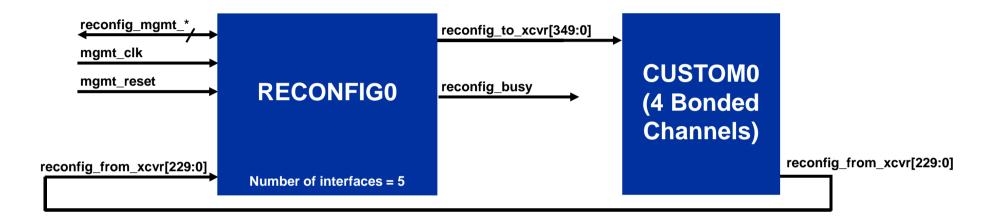

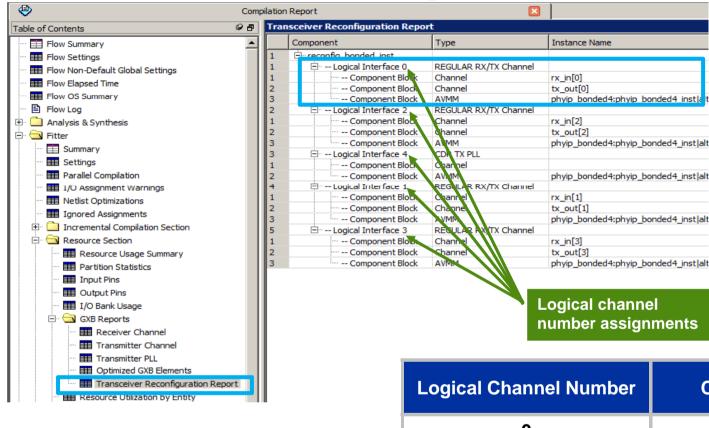

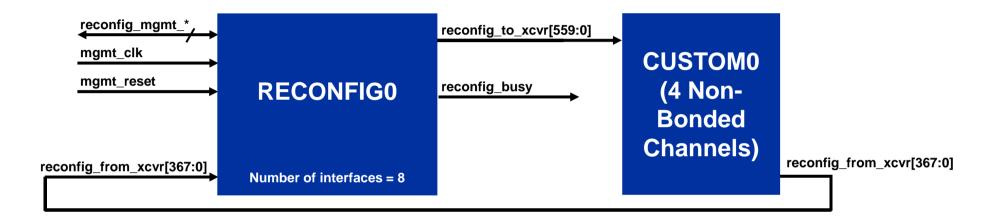

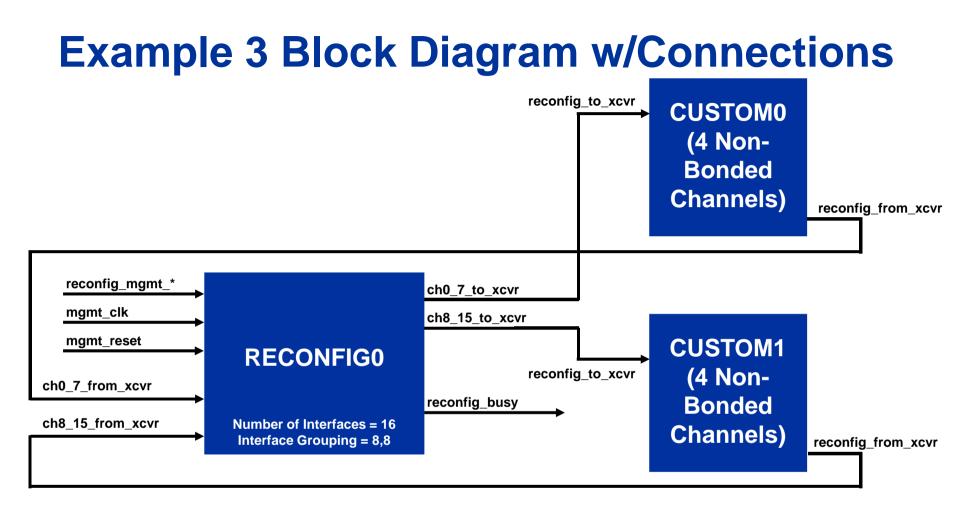

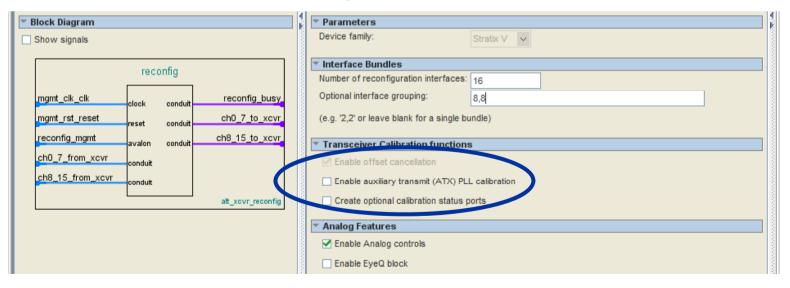

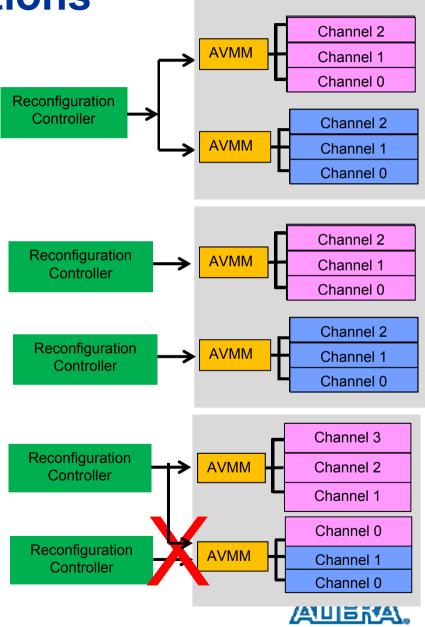

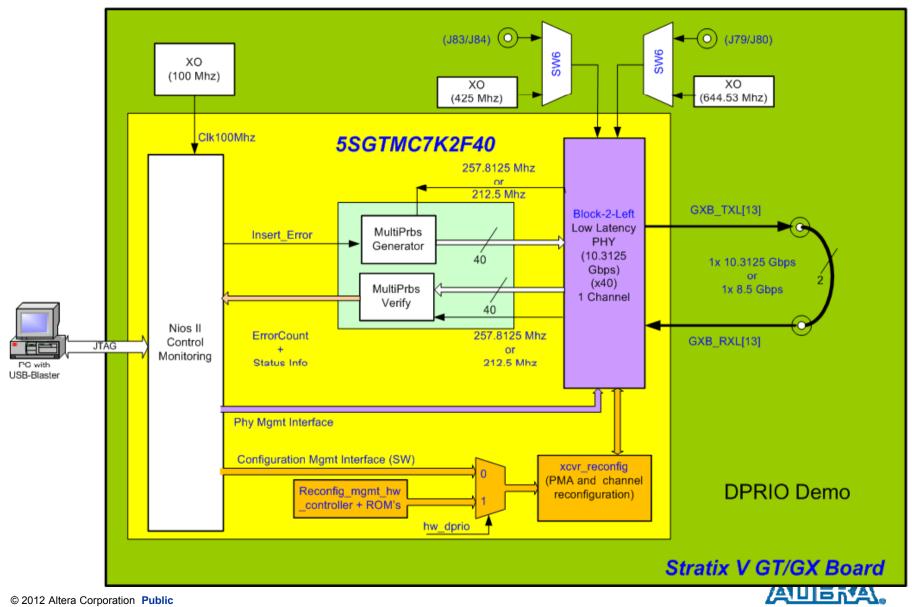

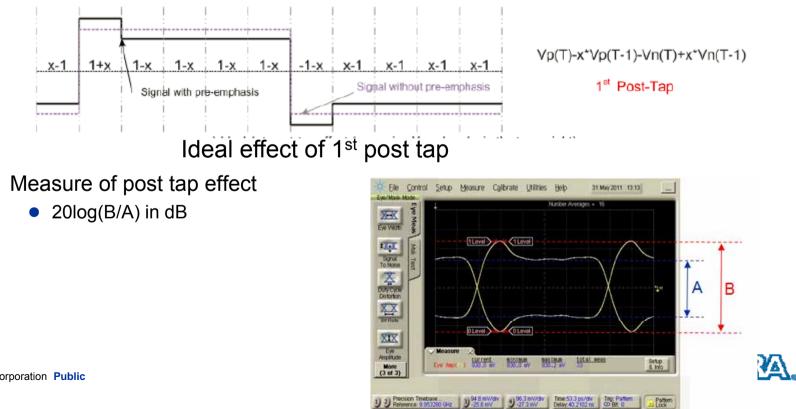

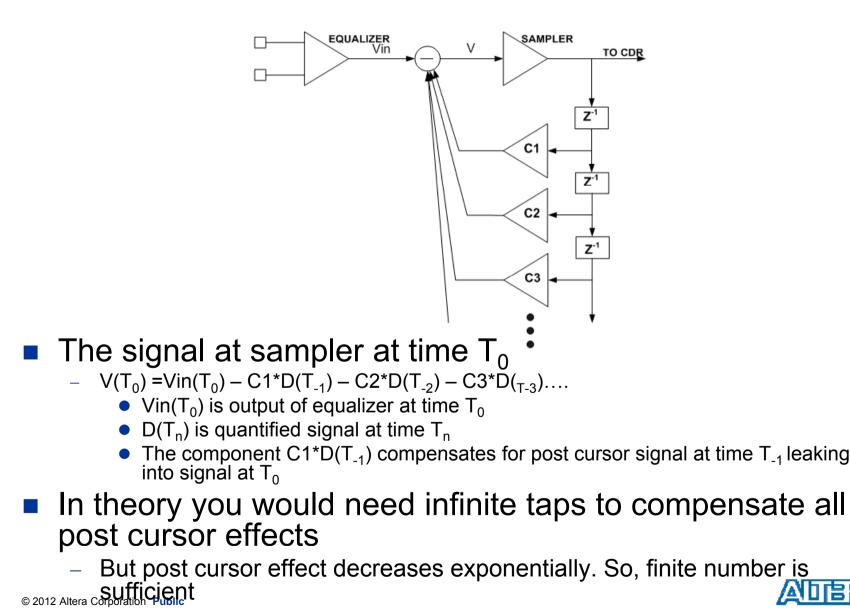

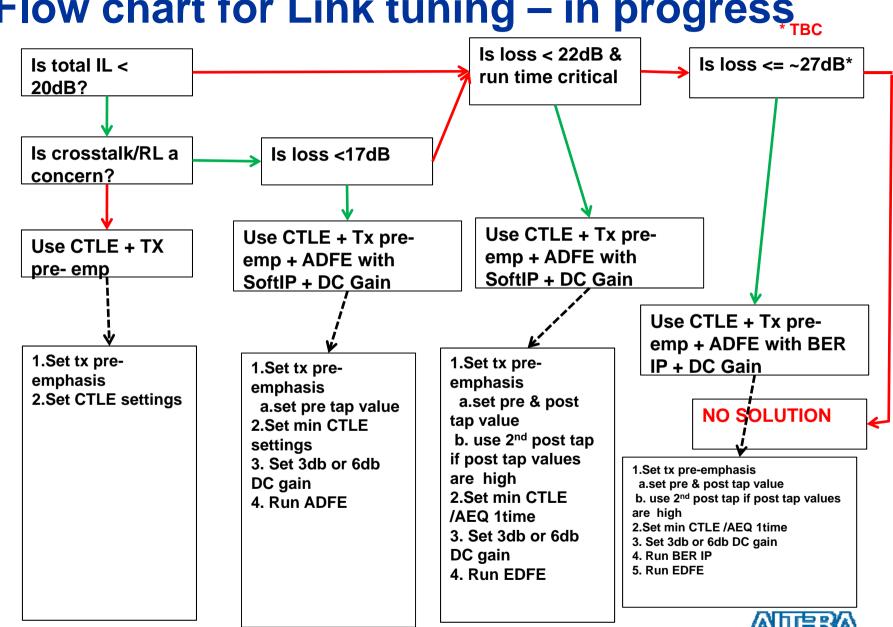

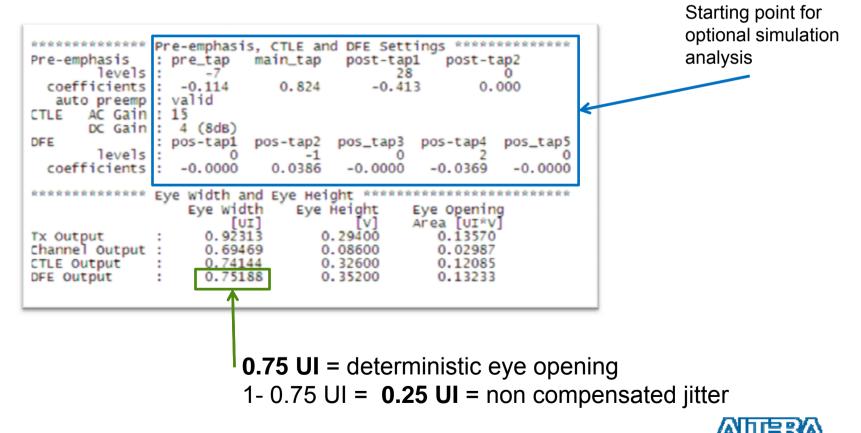

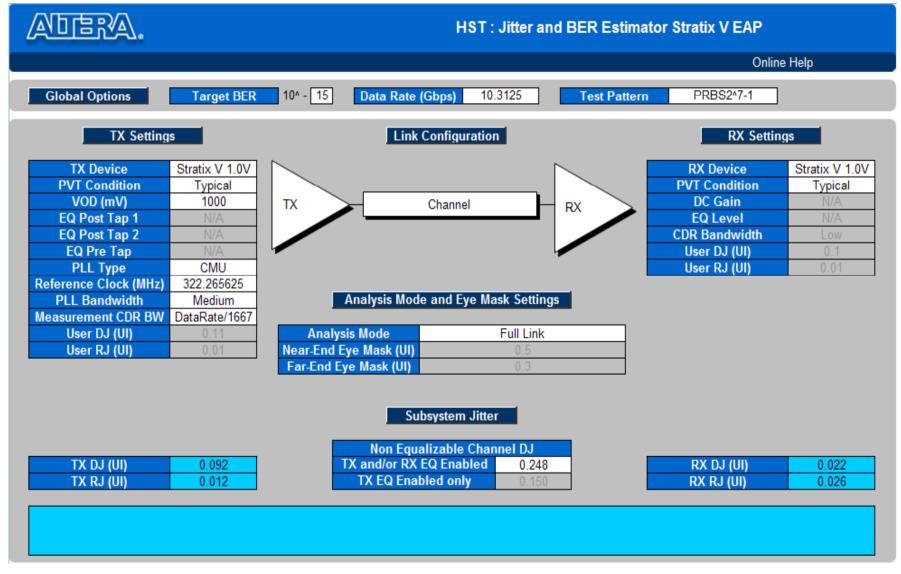

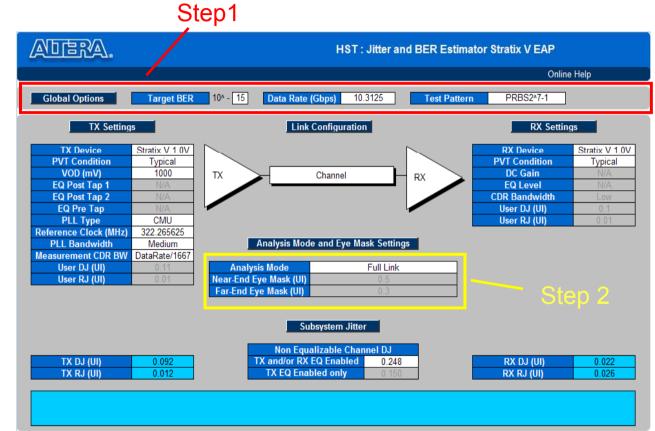

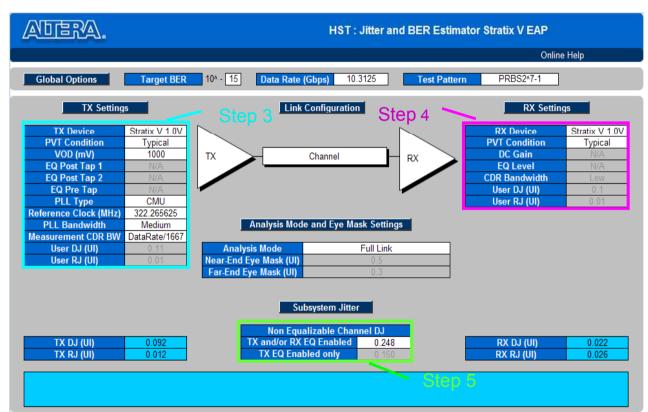

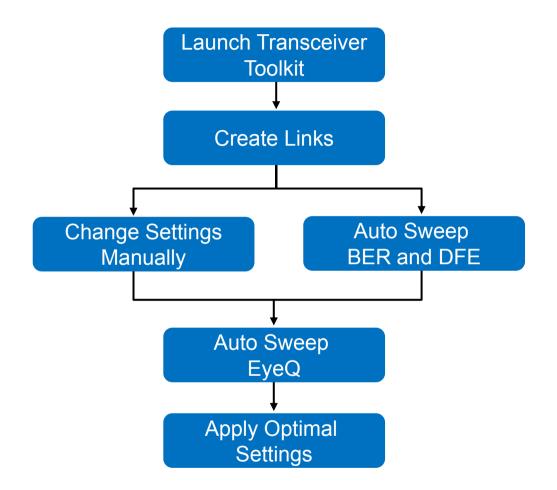

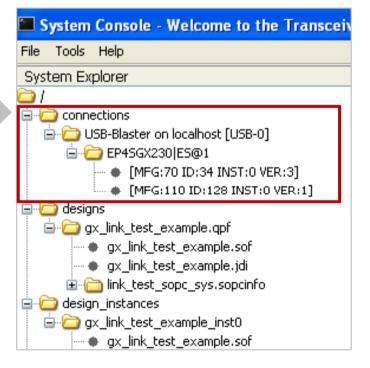

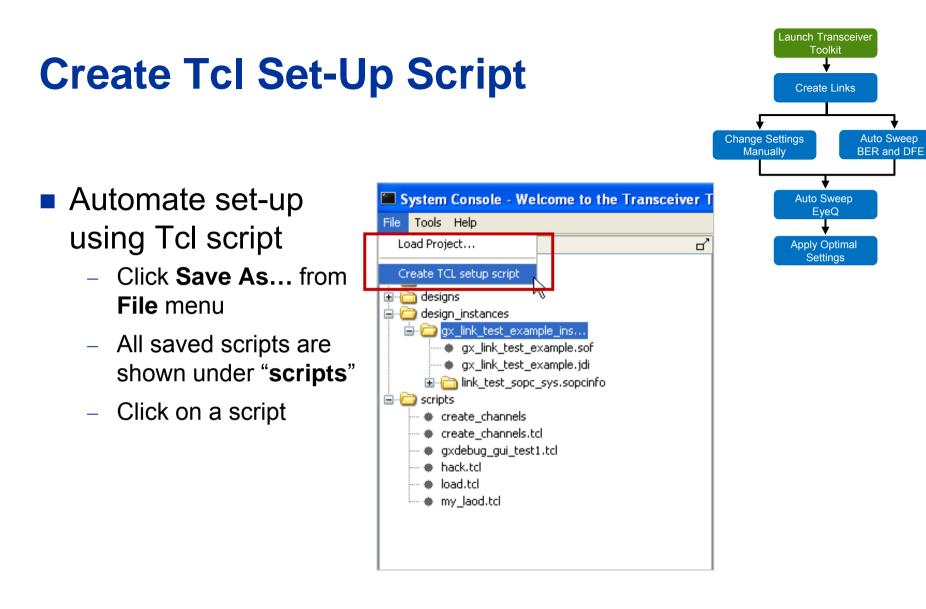

|                            | PCS Reconfiguration         | ✓             | $\checkmark$ | ✓*        |  |