### **Timing Analysis with Timequest**

# **Timing Analysis Basics**

© 2010 Altera Corporation—Confidential

# **Timing Analysis Basics Objectives**

- Define the basic timing parameters used in timing analysis

- Understand the calculations performed by the timing analyzer for reporting timing results

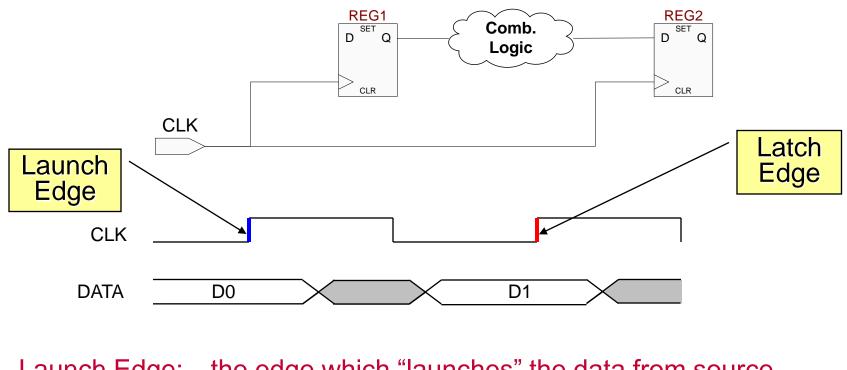

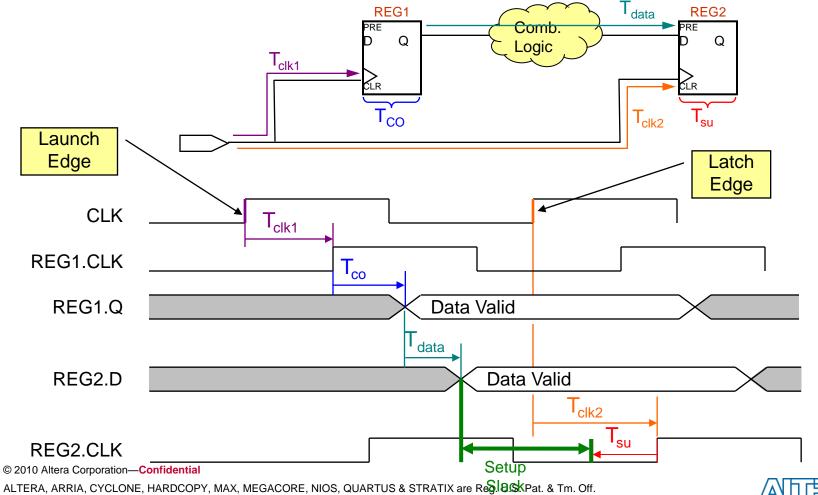

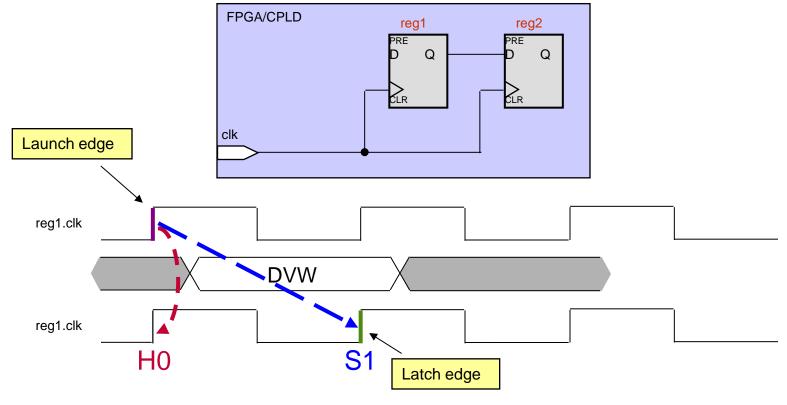

# Launch & Latch Edges

Launch Edge:the edge which "launches" the data from source<br/>registerLatch Edge:the edge which "latches" the data at destination

dge: the edge which "latches" the data at destination register (with respect to the launch edge)

© 2010 Altera Corporation—Confidential

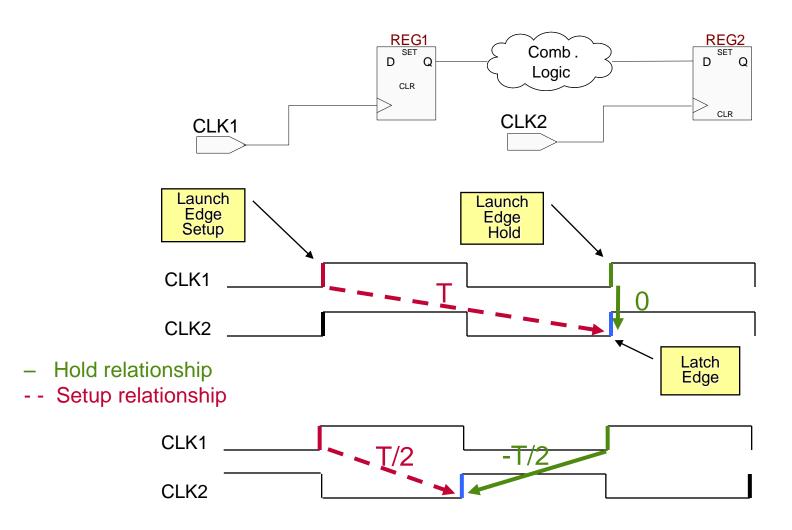

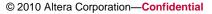

# **Setup & Hold relationships**

© 2010 Altera Corporation—Confidential

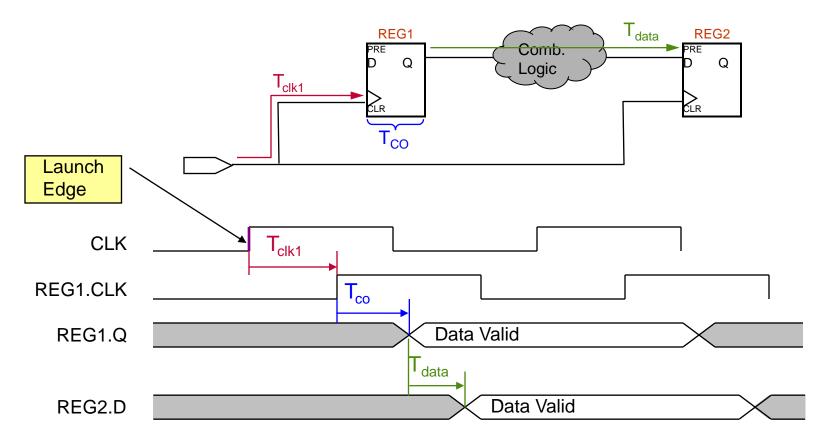

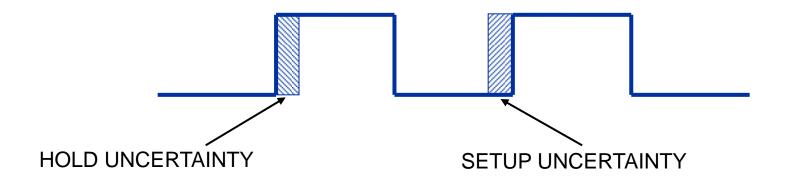

# **Data Arrival Time**

The time for data to arrive at destination register's D input

#### Data Arrival Time = launch edge + $T_{clk1}$ + $T_{co}$ + $T_{data}$

© 2010 Altera Corporation—Confidential

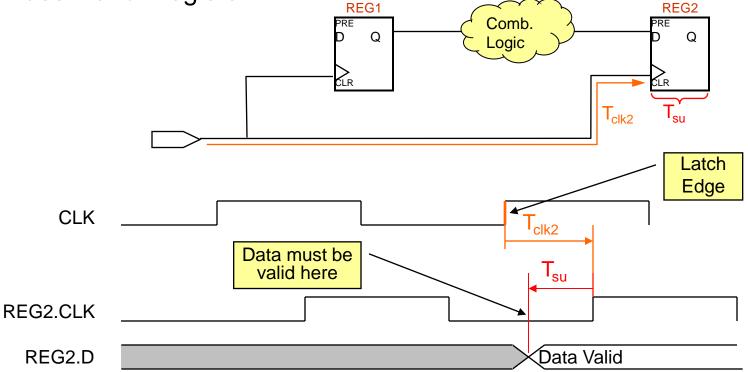

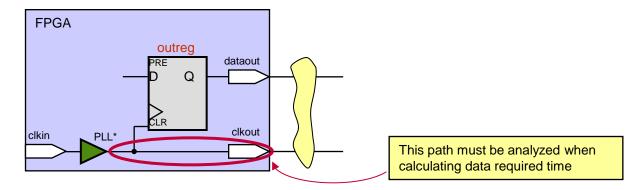

# **Data Required Time - Setup**

The minimum time required for the data to get latched into the destination register

#### Data Required Time = Clock Arrival Time - $T_{su}$ - Setup Uncertainty

© 2010 Altera Corporation—Confidential

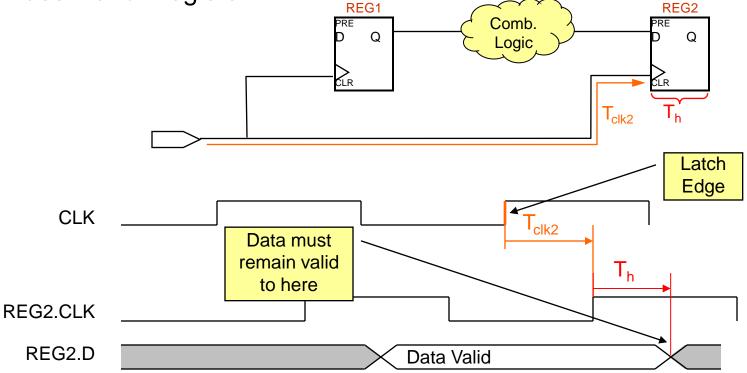

# **Data Required Time - Hold**

The minimum time required for the data to get latched into the destination register

#### Data Required Time = Clock Arrival Time + $T_h$ + Hold Uncertainty

© 2010 Altera Corporation—Confidential

# **Setup Slack**

The margin by which the setup timing requirement is met. It ensures launched data arrives in time to meet the latching requirement.

and Altera marks in and outside the U.S.

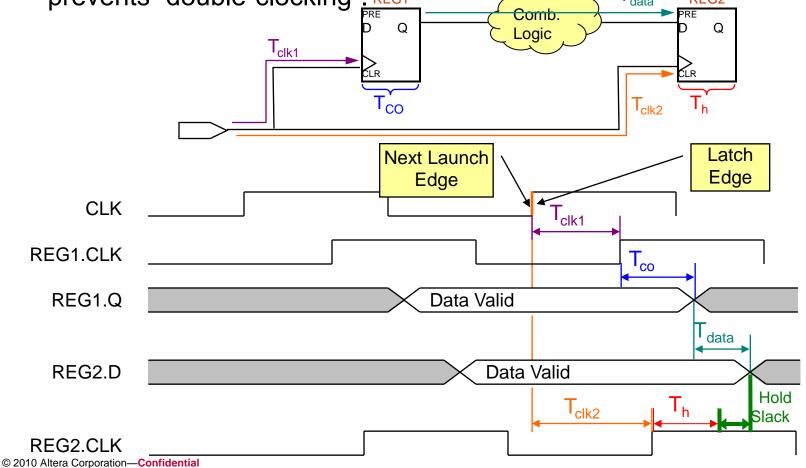

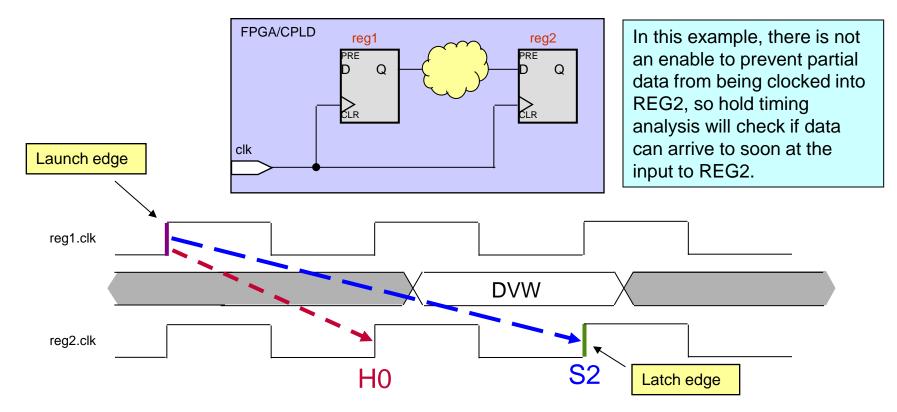

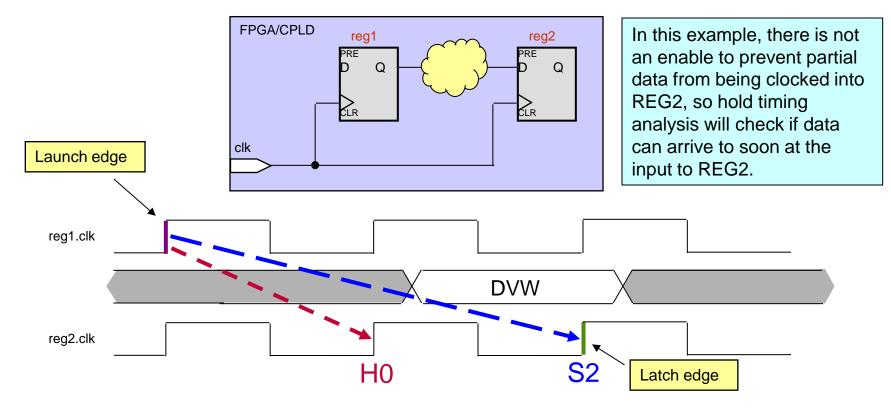

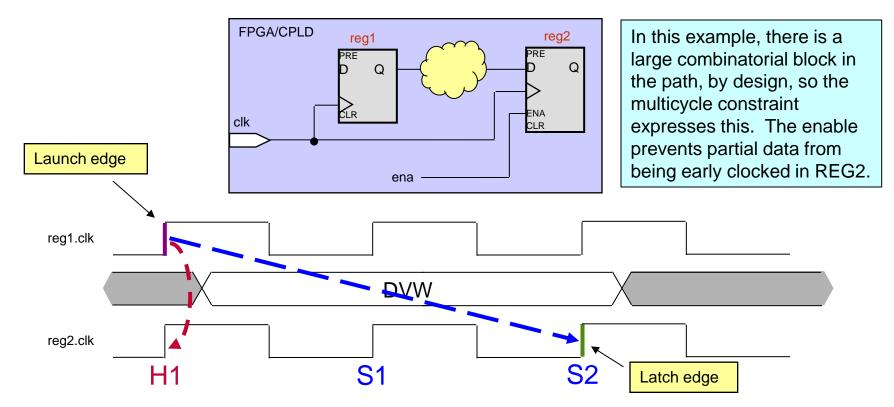

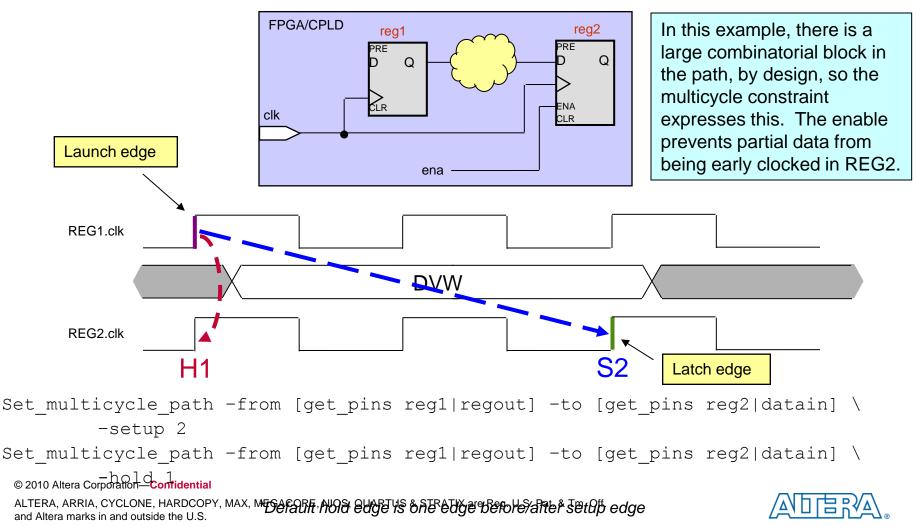

# **Hold Slack**

The margin by which the hold timing requirement is met. It ensures latch data is not corrupted by data from another launch edge. It also prevents "double-clocking". REG1

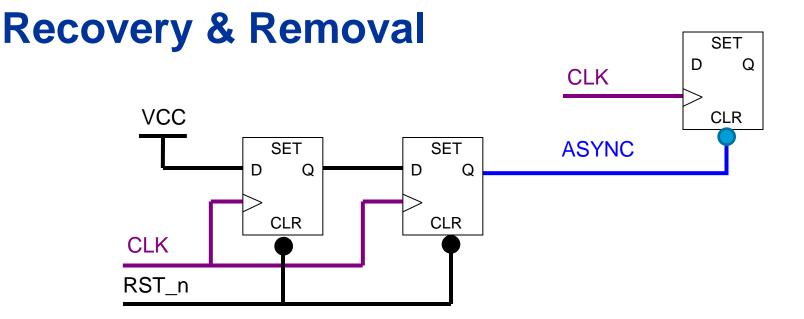

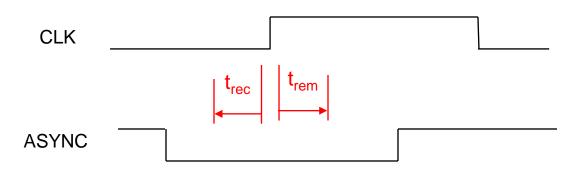

Recovery: The minimum time an asynchronous signal must be deasserted BEFORE clock edge Removal: The minimum time an asynchronous signal must be deasserted AFTER clock edge

© 2010 Altera Corporation—Confidential

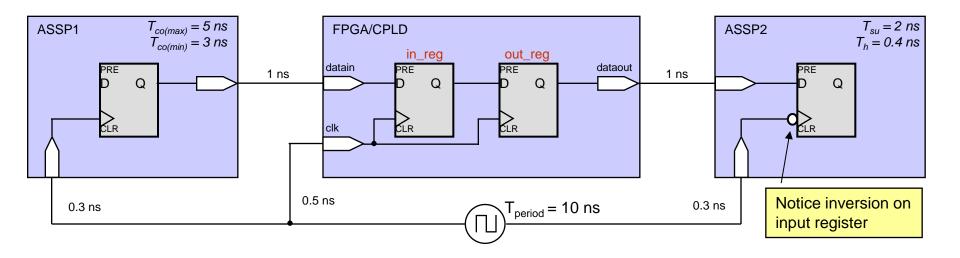

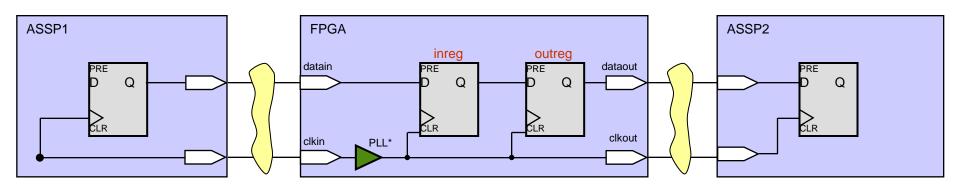

# **Timing Models in Detail**

- Quartus II software models device timing at multiple process voltage temperature (PVT) conditions by default

- Slow corner model

- Indicates slowest possible performance for any single path

- Timing for slowest device at maximum operating temperature and VCCMIN

- Fast corner model

- Indicates fastest possible performance for any single path

- Timing for fastest device at minimum operating temperature and VCCMAX

- 2<sup>nd</sup> slow and 2<sup>nd</sup> fast models (temperature inversion phenomenon)

- Slow timing at minimum operating temperature

- Fast timing at maximum operating temperature

- Available only for Stratix® V devices

- Why analyze for multiple corner timing models?

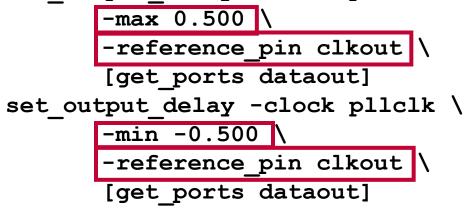

- Ensure **setup** timing is met in the **slow** models

- Ensure hold timing is met in fast model

- Essential for source synchronous interfaces

- Read the following white paper for more information

- <u>http://www.altera.com/literature/wp/wp-01139-timing-model.pdf</u>

© 2010 Altera Corporation—Confidential

### **Timing Analysis with Timequest**

# **TimeQuest Timing Analyzer**

- New timing engine in Quartus II software

- Provides timing analysis solution for all levels of experience

- Features

- Synopsys Design Constraints (SDC) support

- Standardized constraint methodology

- Easy-to-use interface

- Constraint entry

- Standard reporting

- Scripting emphasis

- Presentation focuses on using GUI

© 2010 Altera Corporation—Confidential

# **Timing Analysis Agenda**

- TimeQuest flow

- Timing constraints

- Timing reports

# **Quartus II TimeQuest Settings**

- Add SDC files to TimeQuest Timing Analyzer page of Settings dialog box

- Multicorner analysis checks all process corners in one analysis

- Report worst-case paths in each clock domain

- Select Tcl script to customize report generation

| Settings - test Category:                                                                                                                                                                                                                                                         |                                                                                | Device                                |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|--|--|

| General                                                                                                                                                                                                                                                                           | TimeQuest Timing Analyzer                                                      |                                       |  |  |

| Files<br>Libraries<br>Operating Settings and Conditions<br>Voltage                                                                                                                                                                                                                | Specify TimeQuest Timing Analyzer options. SDC files to include in the project | Click Add to add selected SDC to list |  |  |

| Temperature Compilation Process Settings                                                                                                                                                                                                                                          | File name:                                                                     | Add                                   |  |  |

| Early Timing Estimate<br>Incremental Compilation<br>Physical Synthesis Optimizations<br>EDA Tool Settings<br>Design Entry/Synthesis<br>Simulation<br>Formal Verification<br>Board-Level<br>Analysis & Synthesis Settings<br>VHDL Input<br>Verilog HDL Input<br>Default Parameters | File Name     Type       test.sdc     Synopsys Design Constraints File         | Remove       Up       Down            |  |  |

| Fitter Settings<br>TimeQuest Timing Analyzer<br>Assembler<br>Design Assistant<br>SignalTap II Logic Analyzer<br>Logic Analyzer Interface<br>PowerPlay Power Analyzer Settings<br>SSN Analyzer                                                                                     | Image: Synchronizer identification:       Off                                  | ation                                 |  |  |

#### © 2010 Altera Corporation—Confidential

# **Opening TimeQuest**

Toolbar button 👲

- Tools menu

- Stand-alone mode

- quartus staw

- Command line

| 1 | 🐇 Quartus II - C:/De | veloping_  | Classes/( | )uartusII/Q | II_6_1                       | _update    | s/QII_Test_            | _Designs/TQ/fi | ir_f |

|---|----------------------|------------|-----------|-------------|------------------------------|------------|------------------------|----------------|------|

| 4 | 🔄 File Edit View I   | Project As | signments | Processing  | Tools                        | Window     | Help                   |                |      |

|   | 🗅 🖻 🖩 👹              | Х 🖻 🕻      | l l n c   | `≊ filtref  |                              | A Simulati |                        | •              | 1    |

| 1 | Project Navigator    |            |           | ;           | Run EDA Timing Analysis Tool |            |                        |                |      |

| I | Entity               |            | I/O Reg   | isters N    | 🕦 La                         | unch Desig | gn Space E <u>x</u> pl | orer           |      |

|   | 🛕 Cyclone II: EP2C   | 5F256C6    |           |             | <b>0</b> Ir                  | neQuest Ti | iming Analyze          | r              |      |

|   | 🗄 🛃 filtref          |            | 0 (0)     | 0           |                              | la dina na |                        |                |      |

|   |                      |            |           |             | <u>A</u> C                   | lvisors    |                        |                |      |

© 2010 Altera Corporation—Confidential

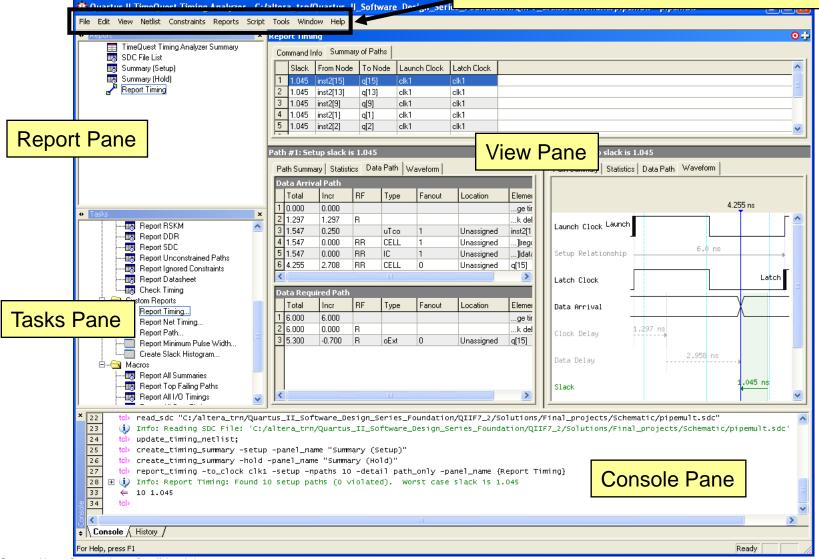

# **TimeQuest GUI**

#### Menu access to all TimeQuest features

© 2010 Altera Corporation—Confidential

# **Tasks Pane**

- Provides quick access to common operations

- Command execution

- Report generation

- Executes most commands with default settings

- Use menus for nondefault settings

© 2010 Altera Corporation—Confidential

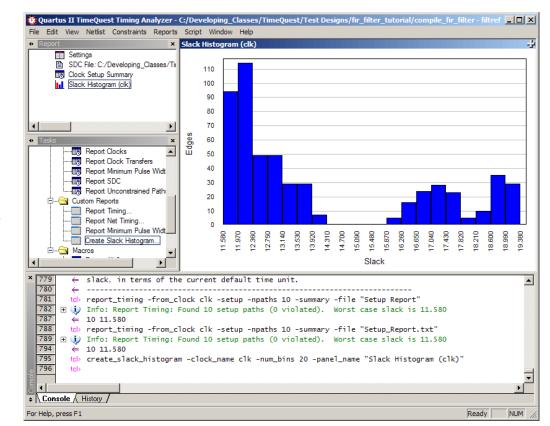

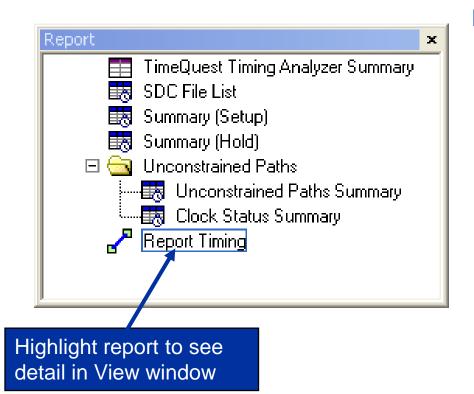

## **Report Pane**

Displays list of generated reports currently available for viewing

- Reports generated by Tasks pane

- Reports generated using report commands

© 2010 Altera Corporation—Confidential

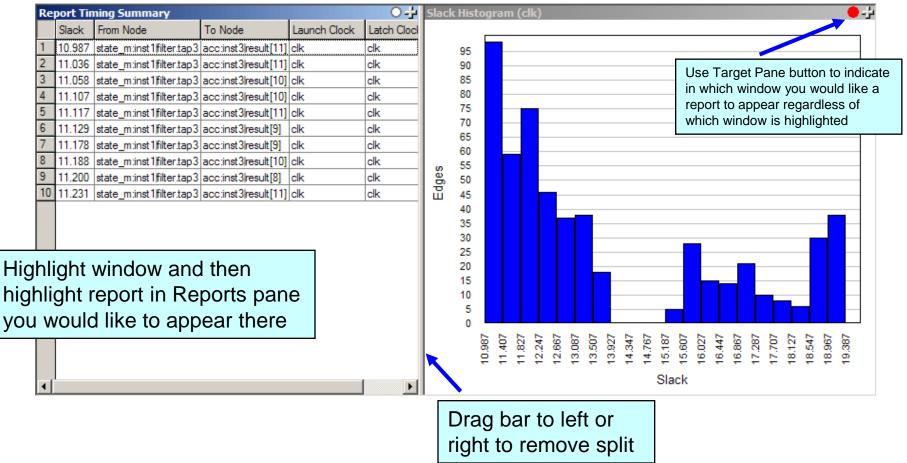

### **View Pane**

# Main viewing area that displays report table contents & graphical results

| Report Timing Summary                                                                                     |                      |            |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                              | P.                                         |

|-----------------------------------------------------------------------------------------------------------|----------------------|------------|----------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------|

| Slack From Node To                                                                                        | Node                 |            |          |                |                | Launch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clock Latch Clock              |                                            |

| 1 1.045 inst2[15] q[15                                                                                    | 5]                   |            |          |                |                | clk1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | clk1                           |                                            |

| 2 1.045 inst2[13] q[13                                                                                    | 3]                   |            |          |                |                | clk1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | clk1                           |                                            |

| 3 1.045 inst2[9] q[9]                                                                                     |                      | ck Histogr | am (clk1 | 3              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | 0+                                         |

| 4 1.045 inst2[1] q[1]                                                                                     |                      | .k Histoyi |          | ·/             |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | <b>6</b> -F                                |

| 5 1.045 inst2[2] q[2]                                                                                     |                      |            |          |                |                | teport Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                | ¢-0                                        |

| 6 1.045 inst2[10] q[10                                                                                    |                      | 325        |          |                |                | Command Info Summary of Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |                                            |

| 7 1.045 inst2[3] q[3]                                                                                     |                      | 300        |          |                |                | Slack From Node To Node L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | aunch Clock Latch Clock        |                                            |

| 8 1.045 inst2[4] q[4]                                                                                     |                      | 275        |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <1 clk1                        | Path Slack Report                          |

| 9 1.045 inst2[14] q[14                                                                                    |                      | 250        |          |                |                | 2 1.045 inst2[13] q[13] c<br>3 1.045 inst2[9] q[9] c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                            |

| 10         1.045         inst2[11]         q[11]           11         1.045         inst2[5]         q[5] |                      | 225        |          |                |                | 4 1.045 inst2[1] q[1] c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |                                            |

|                                                                                                           |                      |            |          |                |                | 5 1.045 inst2[2] q[2] c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | k1 clk1                        | ¥                                          |

|                                                                                                           |                      | 200        |          |                |                | ath #5: Setup slack is 1.045                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                | Path #5: Setup slack is 1.045              |

| 13         1.045         inst2[12]         q[12]           14         1.045         inst2[7]         q[7] |                      | 175 -      |          |                |                | Path Summary Statistics Data Path Waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                | Path Summary Statistics Data Path Waveform |

| 15 1.045 inst2[8] q[8]                                                                                    | л <u>-</u> б'<br>л Ш | 150 -      |          |                |                | Data Arrival Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |                                            |

| 16 1.045 inst2[0] q[0]                                                                                    | -                    | 125        |          |                |                | Total         Incr         RF         Type         Fanout         Loc           1         0.000         0.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ation Element launch edge time | 4.255 ns                                   |

|                                                                                                           | n_mult:lpm_m         |            |          |                |                | 2 1.297 1.297 R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | clock network delay            |                                            |

|                                                                                                           | n_mult:lpm_n         | 100        |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ssigned inst2[2]               | Launch Clock Launch                        |

|                                                                                                           | n_mult:lpm_m         | 75         |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ssigned inst2[2]/regout        | Setup Relationship                         |

|                                                                                                           |                      | 50         |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | signed q[2]                    |                                            |

| <b>Timing Summa</b>                                                                                       | ary 📋                | 25         |          |                |                | Data Required Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                | Latch Clock                                |

| Table                                                                                                     |                      |            |          |                |                | Total         Incr         RF         Type         Fanout         Loc           1         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000         6.000 | ation Element latch edge time  | Data Arrival                               |

| Table                                                                                                     |                      | 0 •        |          | ~              | ~ -            | 2 6.000 0.000 R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | clock network delay            |                                            |

|                                                                                                           |                      | 1.045      | .249     | 1.453          | 1.657<br>1.861 | 3 5.300 -0.700 R oExt 0 Una                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | signed q[2]                    | Clock Delay                                |

|                                                                                                           |                      | ~          | ÷        | <del>.</del> . | ~ ~            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | 2.958 ns                                   |

|                                                                                                           |                      |            |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | Data Delay                                 |

|                                                                                                           | Timing               | g Histo    | ogran    |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | Slack 1.045 ns                             |

|                                                                                                           |                      |            |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |                                            |

|                                                                                                           |                      |            |          |                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                | Data Required                              |

| © 2010 Altera Corpo                                                                                       | oration—Confi        | idential   |          |                |                | J 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |                                            |

#### © 2010 Altera Corporation—Confidential

### **Viewing Multiple Reports**

| Set                                                                | up: clk_x2 | 2          |            |         |        |          |           |             |           |          | +     |       |

|--------------------------------------------------------------------|------------|------------|------------|---------|--------|----------|-----------|-------------|-----------|----------|-------|-------|

| С                                                                  | ommand     | Info Summa | ary of Pat | ns      |        |          |           |             |           |          |       |       |

|                                                                    | Slack      | From Node  | To Nod     | e       | Launch | Clock La | tch Clock |             |           |          | Delay |       |

| 1                                                                  | 0.295      | TDMOUT0    | TDM_m      | uc_out2 | clk_x2 | clk      | _x2       | Click       | & drag    | '+' sign | to p  |       |

| 2                                                                  | 0.295      | TDMOUT0    | TDM_m      | AOUT1   | clk_x2 | clk      | _x2       |             | U         | pane int |       |       |

| 3                                                                  | 0.295      | TDMOUT0    | TDM_m      | AOUT2   | clk_x2 | clk      | _x2       |             |           | •        | ο     |       |

| 4                                                                  | 0.295      | TDMOUT0    | TDM_m      | AOUT3   | clk_x2 | clk      | _x2       | m           | ultiple w | vindows  | O     |       |

| 5                                                                  | 0.295      | TDMOUT0    |            | AOUT4   | clk_x2 |          | _x2       | 5.500       |           | .500     | 2.020 |       |

| 6                                                                  | 0.295      | TDMOUT0    | _          | AOUT5   | clk_x2 |          | _x2       | 3.500       |           | .388     | 2.620 | _     |

| 7                                                                  | 0.295      | TDMOUT0    |            | AOUT6   | clk_x2 |          | _x2       | 3.500       |           | .388     | 2.620 |       |

| 8                                                                  | 0.295      | TDMOUT0    | _          | AOUT7   | clk_x2 |          | _x2       | 3.500       |           | .388     | 2.620 |       |

| 9                                                                  | 0.295      | TDMOUT0    | TDM_m      | AOUT8   | clk_x2 | Clk      | _x2       | 3.500       |           | .388     | 2.620 | -     |

| Path #1: Setup slack is 0.295 Path #1: Setup slack is 0.295        |            |            |            |         |        |          |           |             |           |          |       |       |

|                                                                    |            |            |            |         |        |          |           |             | Waveform  | 1        |       |       |

| Da                                                                 | ata Arriv  | al Path    |            |         |        |          |           |             |           |          |       |       |

|                                                                    | Total      | Incr       | RF         | Туре    | Fanout | Location |           |             |           |          |       |       |

| 1                                                                  | 0.000      | 0.000      |            |         |        |          |           |             |           |          |       |       |

| 2                                                                  | 0.404      | 0.404      |            |         |        |          |           | 1 auna      |           |          |       |       |

| 3                                                                  |            | 000.0 000  |            |         |        |          | Launch I  | Clock Laune | 201       |          |       |       |

| 4                                                                  | i i        | 000 000    |            | 1       | 1      | PIN F?   | <u> </u>  |             | 1         | 3.5      | ns    |       |

| Image: Data Required Path     Image: Setup Relationship     3.5 ns |            |            |            |         |        |          |           |             |           |          |       |       |

|                                                                    | Total      | Incr       | RF         | Туре    | Fanout | Location | Latch C   | lock        |           |          |       | Latch |

| 1                                                                  | 3.500      | 3.500      |            |         |        |          |           |             |           |          |       |       |

| 2                                                                  | ⊡ 3.516    | 0.016      |            |         |        |          | Data Ari  | rival       |           |          |       | X     |

| 3                                                                  | - 3.5      | 500 0.000  |            |         |        |          | _1        |             |           | -        |       |       |

| 4                                                                  |            | 500 0.000  | J          |         | 1      |          | Clock D   | elay        | 0.404 ns  |          |       | -     |

#### © 2010 Altera Corporation—Confidential

# **Viewing Multiple Reports Example**

#### View pane split into two side-by-side windows

© 2010 Altera Corporation—Confidential

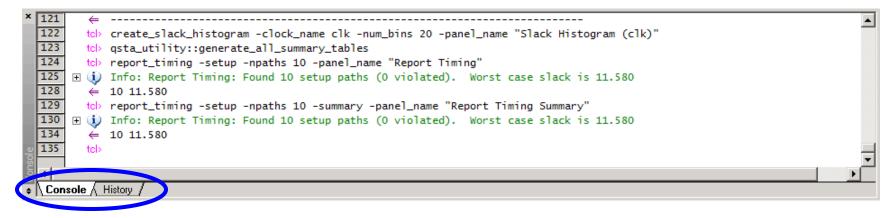

### **Console pane**

- Allows direct entry and execution of SDC & Tcl commands

- Displays equivalent of command executed by GUI

- Displays TimeQuest output messages

- History tab records all executed SDC & Tcl commands

© 2010 Altera Corporation—Confidential

# **Steps to Using TimeQuest**

- 1. Generate timing netlist

- 2. Read SDC file

- 3. Update timing netlist

- 4. Generate timing reports

# 1) Generate Timing Netlist

- Creates timing netlist (i.e. database) based on compilation results

- Post-synthesis (mapping) or post-fit

- Worst-case (slow) or best-case (fast) timing model

To execute:

| Create Timing Netlist                                                                                           | Netlist menu                                                                      | Tacka    |                                      |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------|--------------------------------------|

| Input netlist     Post-fit                                                                                      | Delay model<br>Slow corner<br>Speed grade:                                        |          | ng Netlist                           |

| C Post-map<br>Tcl command: create_tir                                                                           | <ul> <li>○ Fast corner</li> <li>☐ Zero IC delays</li> <li>ming_netlist</li> </ul> |          | ports<br>max Summary<br>etup Summary |

|                                                                                                                 | OK Cancel Help<br>Tcl equivalent of com                                           | Report R | emoval Summary                       |

| © 2010 Altera Corporation—Confident<br>ALTERA, ARRIA, CYCLONE, HARDCO<br>and Altera marks in and outside the U. | DPY, MAX, ME TCI: create_timing_ne                                                | etlist   |                                      |

# **Specifying Operating Conditions**

- Perform timing analysis for different delay models without recreating the existing timing netlist

- Takes precedence over already generated netlist

- Required for selecting slow, min. temp. model and other models (industrial, military, etc.) depending on device

- Use get available operating conditions to see available conditions for target device

|                                                                                                                      | Set Operating Conditions                                |    |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----|

|                                                                                                                      | C User specified default operating conditions:          |    |

| Quartus II TimeQuest Timing Analyzer - 0                                                                             | 7_slow_1200mv_100c<br>7_slow_1200mv40c                  |    |

| File Edit View Netlist Constraints Reports Scr                                                                       | MIN_fast_1200mv40c                                      |    |

| Report     Create Timing Netlist                                                                                     |                                                         |    |

| Time Set Operating Conditions                                                                                        | Other available operating conditions:                   |    |

| 🕀 🛄 Adva Update Timing Netlist                                                                                       | 7 slow 1200mv 85c                                       |    |

| 🗆 🔄 Unco Delete Timing Netlist                                                                                       | 7_slow_1200mv_0c<br>MIN_fast_1200mv_0c                  |    |

|                                                                                                                      |                                                         |    |

|                                                                                                                      |                                                         |    |

|                                                                                                                      |                                                         |    |

| © 2040 Alters Comparties Confidential                                                                                | SDC command: set_operating_conditions 7_slow_1200mv_85c |    |

| © 2010 Altera Corporation—Confidential                                                                               |                                                         | ~  |

| ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATI><br>and Altera marks in and outside the U.S. |                                                         | 7* |

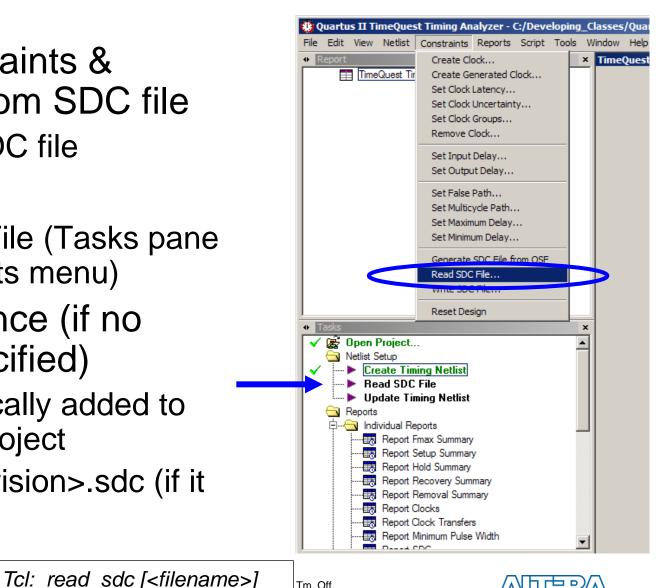

# 2) Read SDC File

- Reads constraints & exceptions from SDC file

- Skip if no SDC file

- Execution

- Read SDC File (Tasks pane) or Constraints menu)

- File Precedence (if no filename specified)

- Files specifically added to Quartus II project

- <current\_revision>.sdc (if it exists)

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, M and Altera marks in and outside the U.S.

# 3) Update Timing Netlist

- Applies SDC constraints/exceptions to current timing netlist

- Generates warnings

- Undefined clocks

- Partially defined I/O delays

- Combinatorial loops

- Update timing netlist after adding any new constraint

- Execution

- Update Timing Netlist (Tasks pane or Netlist menu)

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACOR and Altera marks in and outside the U.S.

Tcl: update\_timing\_netlist

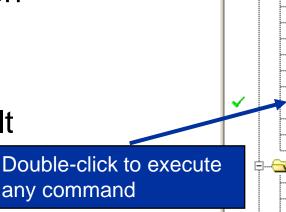

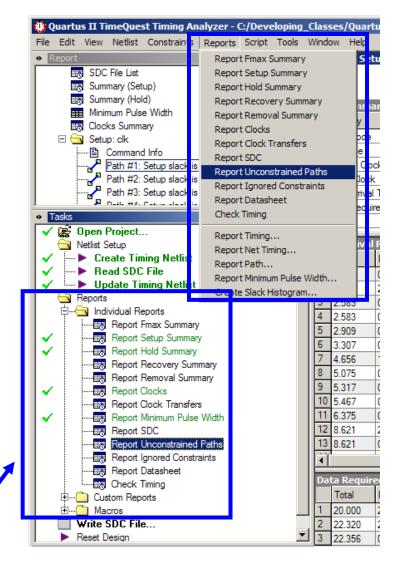

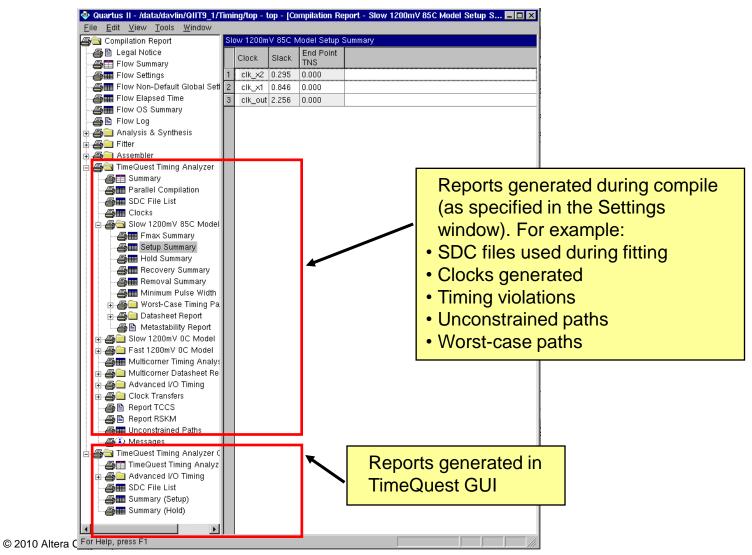

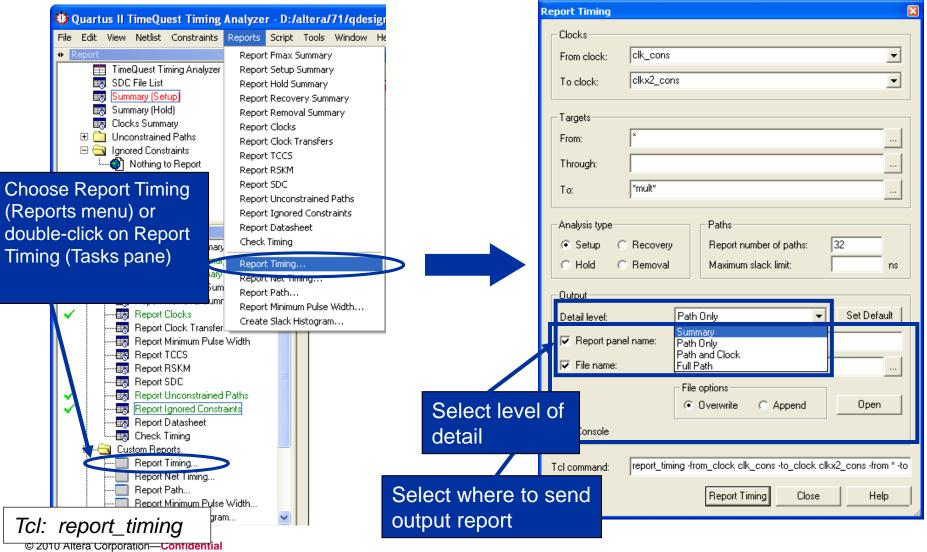

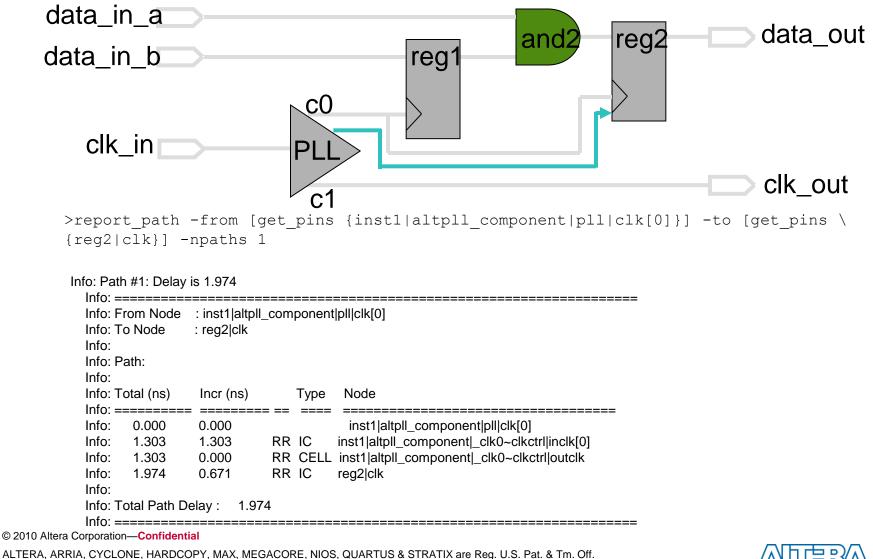

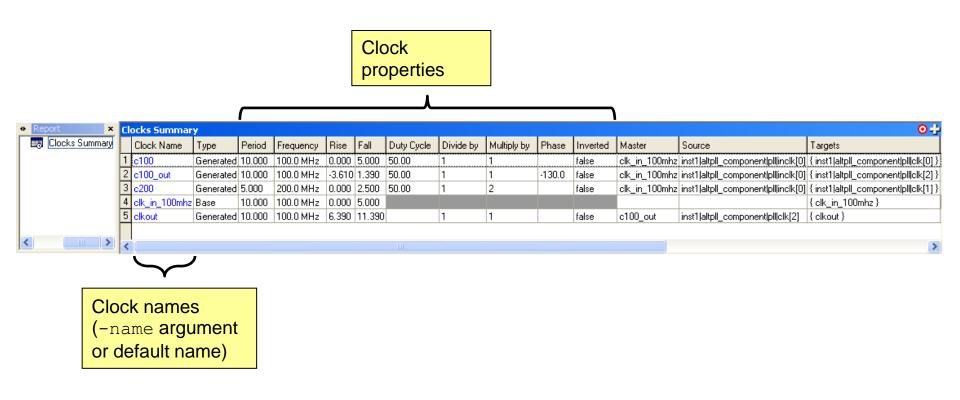

# 4) Generate Timing Reports

- Verify timing requirements and locate violations

- Check for fully constrained design or ignored timing constraints

- Two Methods

- Tasks pane

- Automatically creates/updates netlist & reads default SDC file if needed

- Reports menu

- Must have valid netlist to access

- Tasks pane or Reports menu

Double-click on

individual report

© 2010 Altera Corporation—Confidential

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEG and Altera marks in and outside the U.S.

# **Reset Design Command**

- Located in Tasks pane

- Flushes <u>all</u> timing constraints from current timing netlist

- Functional Tcl equivalent: delete\_timing\_netlist command followed by create\_timing\_netlist

- Uses

and Altera marks in and outside the U.S.

• "Re-starting" timing analysis on same timing netlist applying different constraints or SDC file

# **Steps to Using TimeQuest (Review)**

- 1. Generate timing netlist

- 2. Read SDC file

- 3. Update timing netlist

- 4. Generate timing reports

(Optionally)

- 5. Modify SDC file

- 6. Reset Design and go back to step 2

© 2010 Altera Corporation—Confidential

# **Timing Analysis Agenda**

- TimeQuest flow

- Timing constraints

Timing reports

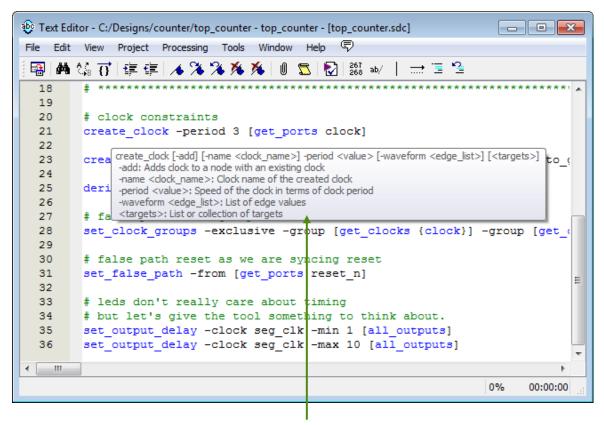

# SDC File Editor = Quartus II Text Editor

- Use Quartus II editor to create and/or edit SDC

- SDC editing unique features (for .sdc files)

- Access to GUI dialog boxes for constraint entry (Edit ⇒ Insert Constraint)

- Syntax coloring

- Tooltip syntax help

- SDC templates

TimeQuest File menu  $\Rightarrow$  Open/New SDC File Quartus II File menu  $\Rightarrow$  New  $\Rightarrow$  Other Files

Place cursor over command to see tooltip

© 2010 Altera Corporation—Confidential

# **SDC File Editor (cont.)**

| т    | ext Ed   | itor - C:/Designs/counter/top_                             | counter - top_count       | er - [top_counter.sdc]                | Construct an SDC file using                                                          |

|------|----------|------------------------------------------------------------|---------------------------|---------------------------------------|--------------------------------------------------------------------------------------|

| File | Edit     | View Project Processing                                    | Tools Window H            | Help 🛡                                | Ū                                                                                    |

|      | ß        | Undo                                                       | Ctrl+Z                    | 🔯   267 ab/   🔜 🗉 😩                   | TimeQuest graphical                                                                  |

|      | CH.      | Redo                                                       | Ctrl+Y                    | *****                                 | constraint creation tools                                                            |

|      | *        | Cut                                                        | Ctrl+X                    | 2009 Altera Corporatio                |                                                                                      |

|      | Pa       | Сору                                                       | Ctrl+C                    | PY, MAX, MEGACORE, NIOS               | 😵 Create Clock                                                                       |

|      | Ē.       | Paste                                                      | Ctrl+V                    | and Altera marks in and               |                                                                                      |

|      | X        | Delete                                                     | Del                       | n is provided on as "as               | Clock name: clk                                                                      |

|      |          | Select All                                                 | Ctrl+A                    |                                       | Period: 10.000 ns                                                                    |

| 1    | 酋        | Find                                                       | Ctrl+F                    |                                       | Waveform edges                                                                       |

| 1    | M.,      | Find Next                                                  | F3                        |                                       | waveronn euges                                                                       |

| 1    | 0        | Find Matching Delimiter                                    | Ctrl+M                    | ins the timing constrai               | Rising: 3 ns                                                                         |

| 1    | β        | Replace                                                    | Ctrl+H                    |                                       | Falling: 8 ns                                                                        |

| 1    | -        | Go To                                                      | Ctrl+G                    | nitial Revision                       | 3.00 8.00 10.00                                                                      |

| 1    | t 🗐      | Increase Indent                                            |                           | ****************                      | Targets: [get_ports {dk}]                                                            |

| 1    |          | Decrease Indent                                            | Shift+Tab                 |                                       |                                                                                      |

| 2    |          | Comment Selection                                          |                           | clock]                                | SDC command: create_clock -name clk -period 10.000 -waveform {3 8} [get_ports {clk}] |

| 2    | 1-4      | Uncomment Selection                                        |                           | ll_7seg_inst altpll_com               | Insert Cancel Help                                                                   |

| 2    |          | Insert File                                                | Ctrl+E                    |                                       |                                                                                      |

| 2    | <b>_</b> | Insert Template                                            |                           |                                       |                                                                                      |

| 2    |          | Insert Constraint                                          | •                         |                                       |                                                                                      |

| 2    |          | Insert Constraint                                          |                           | Create Clock                          |                                                                                      |

| 3    | 1 1      | Toggle Bookmark                                            | Ctrl+F2                   | Set Clock Latency                     | 🕸 Text Editor - C:/Designs/counter/top_counter - top_counter - [top_counter.sdc]*    |

| 3    |          | Jump to Next Bookmark                                      | F2                        | Set Clock Uncertainty                 | File Edit View Project Processing Tools Window Help 🗟                                |

| 3    | 1 🖌 🗌    | Jump to Previous Bookmark<br>Clear All Bookmarks (Current) | Shift+F2<br>Ctrl+Shift+F2 | Set Clock Groups                      | ♣ ५% ♂   幸 幸   ★ ≫ ≫ ≫   ∅                                                           |

| 3    |          | Clear All Bookmarks (All Files)                            | Curtonint+2               | Remove Clock                          | 1<br>2                                                                               |

| 3    |          |                                                            |                           | Set Input Delay                       | 2 Gereate_crock -mame crk -period 10.000 -waverorm (3.8) [get_ports (crk/]           |

|      |          | Replace Tabs With Spaces                                   |                           | Set Output Delay                      |                                                                                      |

|      |          |                                                            |                           |                                       | 0% 00:00:00                                                                          |

|      |          |                                                            |                           | Set False Path<br>Set Multicycle Path |                                                                                      |

|      |          |                                                            |                           | Set Maximum Delay                     | Constraints inserted at cursor                                                       |

|      |          |                                                            |                           | Set Minumum Delay                     | TUS & STRATIX are Reg. U.S. Pat. & Thoefation                                        |

|      |          |                                                            |                           |                                       |                                                                                      |

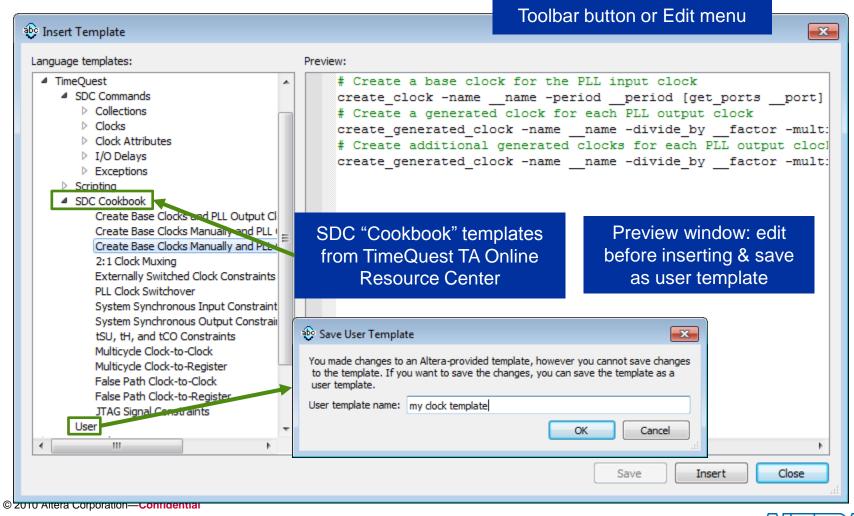

# **SDC Templates**

### Quickly add customized constraint templates

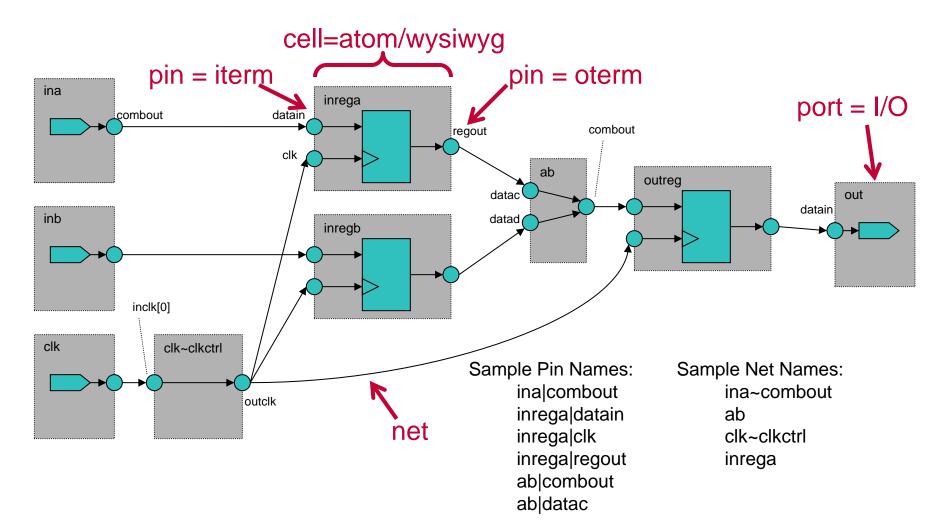

# **SDC Netlist Terminology**