#### Table ronde

# Testabilité et tests des chips

Gisèle Martin-Chassard - Ecole de microélectronique Porquerolles - mai 2007

#### Testabilité et tests des chips :

- La testabilité → doit être prévue à l'intérieur des chips

- 2. Le test de debugging du chip : la carte de test, le soft, les standards de communications ...

- 3. Les tests automatisés pour les séries

#### 1 - La testabilité à l'intérieur des chips

- > Plus les chips sont complexes, plus l'accès aux points internes est important.

- > La sortie des points de mesure ne doit pas perturber le fonctionnement normal (simuler ces points avec le pad)

- La génération des vecteurs de test pour la partie numérique.

> ...

### Testabilité (I)

#### Comment insérer des points de mesures :

- Ajouter un pad pour mesure:

Capa du pad (1 à 2 pF) → buffer nécessaire

Self de bonding (10nH)

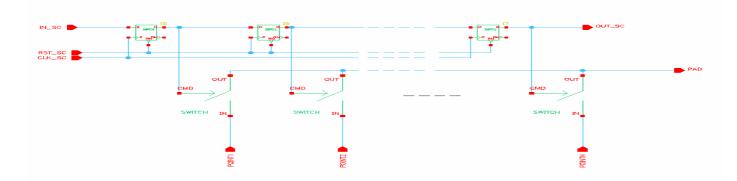

- ➤ Chaîner plusieurs points à l'aide de switches pilotés par registre à décalage vers un pad :

### Testabilité (II)

#### Astuces de layout :

- Séparer les alimentations blocs par blocs :

- · Pour connaître le courant par bloc

- Pour éteindre un bloc seul

- Ajouter des switches pour isoler les points de mesure :

- NMOS de  $0.4/0.35 \rightarrow Ron \approx 4K$

- PMOS de  $0.4/0.35 \rightarrow Ron \approx 20K$

### 2 - Le test de debugging du chip

- > Cartes de test de plus en plus complexes

- ➤ Beaucoup de « slow control » à l'intérieur du chip.

- > De plus en plus de numérique intégré.

- > Comment caractériser les ADCs?

- > Peut-on mutualiser certains tests?

# Exemple : carte de test de MAROC2

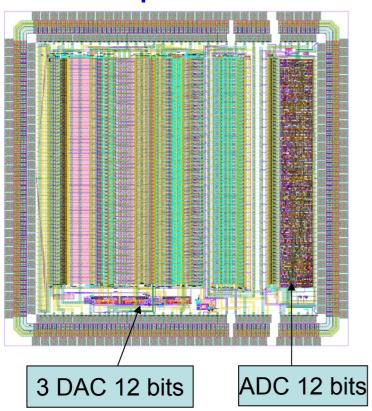

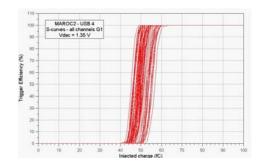

#### Le chip MAROC2

Chip de lecture de PM multianode :

- 64 voies de front-end

- 1 sortie charge multiplexée

- 1 sortie ADC

- 64 sorties trigger

- 3 DACs pour charger seuils

- 540 points de slow control

- → Pierre Barrillon

## Tests de caractérisation de MAROC : la carte de test

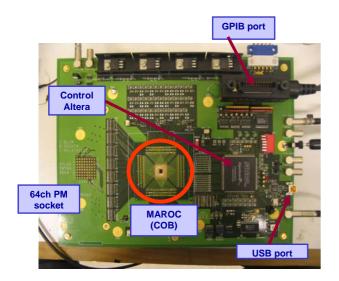

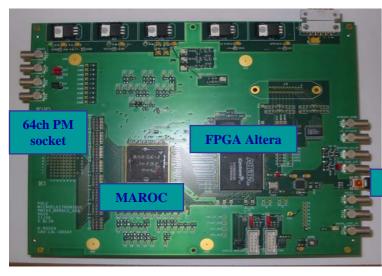

- Les deux versions de l'ASIC MAROC (Multi-Anode Read-Out Chip) ont ou sont testées grâce à des cartes de tests conçues au LAL

- Ces cartes comportent :

- ✓ Le chip MAROC (dans un package + socket, monte sur la carte ou dans un package soudé sur la carte)

- ✓ Un FPGA (Altera)

- ✓ Un port USB (et un port GPIB)

- ✓ Nombreuses entrées et sorties de test

- Un générateur de signal est utilisé pour simuler le signal d'un PM à travers une capa

**Port USB**

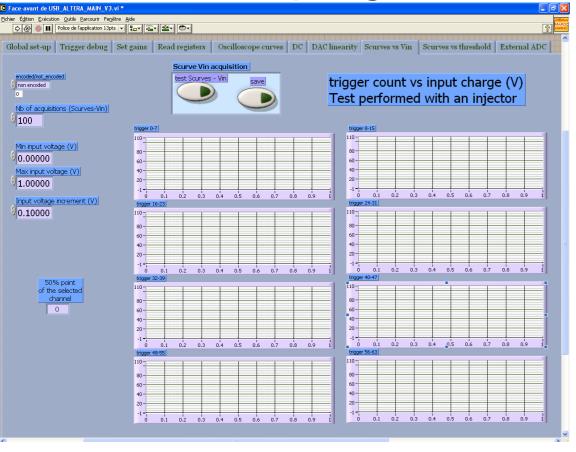

# Tests de caractérisation de MAROC : le programme de tests

- Programme LabVIEW (7.1)

- Onglet de configuration des registres (Slow control)

- Onglets de debugg

- Onglets de test :

- → mesure du DC (multimètre)

- → linéarité du DAC

- → S-curves

- → mesure de la charge

- **→** ...

- Sauvegarde des données pour analyse off line

- → GPIB : très stable, transportabilité moins aisée

- → USB : stabilité problématique, standard incontournable

#### 3 - Les tests automatisés pour les séries

- > Bancs de test utilisés pour LHC :

- > bilan

- > quid de l'utilisation du robot?

- >Prospectives sur les besoins futurs :

- > ILC: tests sous pointes des wafers

- > vecteurs de test pour la partie numérique

- >...