## Les ROC chips

Laboratoire: UMS OMEGA

Sujet : aperçu des circuits complets réalisés par le pôle OMEGA: un nom de contact est associé à chaque circuit

### The ROC chips

#### HARDROC / MICROROC

HARDROC is a 64-channel front-end ASIC designed to readout negative fast (<1ns) and short (<10ns) current pulses from various detectors (Multi Anode</p> Photo Multipliers Resistive Plate Chambers HARDROC provides a semidigital readout with three thresholds tunable between 10 fC up to 10 pC and integrates a 128-deep digital memory to store the 2 x 64 disc. well as the bunch crossing identification coded over 24 bits

The three thresholds are set by three integrated 10-bit DACs. The gain of each channel can be tuned individual. from 0 to 2 over 8 bits, allowing the compensation of nonuniformity between the 64 detector channels. Each channel can auto trigger down to 5 fC which correspond

A multiplexed charge measurement up to 10pC is integrated and can be dais chained, 872 slow control parameters allow versatility and various settings. The power consumption is about 1.5 mW/channel and the chip can be fully powerulsed allowing a significant power reduction by disabling unused blocks. MICROROC is a variant of HARDROC and integrates an ultra low noise ch oreamp (0.1 fC for a detector capacitor of 80 pF) allowing to set the threshold

#### Contact : Nathalie Seguin-Moreau

SKIROC2 is a 64-channel front-end ASIC designed to readout silicon PIN diodes. Each channel is made of a variable-gain and low-noise charge preamplifier followed by two shapers - one with a gain of 1 and the other with a gain of 10 - to provide a charge measurement from 0.2 fC up to 10 pC. A time tagging is performed by a 12-bit TDC ramp. The charges and times are stored in a 15-depth Switched Capacitor Arrays (SCA), the values of which are converted by a multi-channel 12-bit Wilkinson ADC and sent to an integrated 4 Kbytes

memory. The analog value of the charge is also available on an output pin The trigger chain is composed of a high gain fast shaper down to 0.2 fC. Thresholds of the 64 discriminators are se by a common 10-bit DAC and an individual 4-bit DAC pe channel. Each discriminator output is sent to an 8-bit dela cell (delay time tunable between 100 ns and 300 ns) to provide the Hold signal for the SCA cells of the slo channel. The power consumption is about 1.5 mW/channel and each stage can be individually shut down when no used. 616 slow control parameters are available to s

#### Contact : Stéphane Callier PARISROC

Parisroc is a 16-channel front-end ASIC designed to readout photomultiplies tubes (PMTs) in large scale applications such as water Cerenkov experiments. It concept of the ASIC is to combine an auto-trigger chip to 16 PMTs to obtain an autonomous macro-cell for large area of detection

An adjustment of the gain of each channel compensates the gain variation of the PMTs and allows to use only one HV cable for the 16 PMTs. In the ASIC, the 16 channels are totally independent. In each channel, the auto-trigger starts the charg and time measurements which are then converted and stored.

Only the hit channels are read out by one serialized output. The time measurement is done by a 24-bit counter at 10MHz for the coarse time and a time to amplitude converter for the fine time, giving with a resolution better than 1 ns. The charge measurement is done by a 2 gain preamplifier followed by a shaper with variable shaping times (25ns, 50ns or 100ns). Charge and fine time values are converted by a 10 bit ADC.

Contact : Gisèle Martin-Chassard

#### MAROC

MAROC for "Multi Anode Read Out Chip" is a 64-channel chip designed to readout negative fast input current pulses such as those provided by Multi Anode Photo Multipliers. Each channel provides a 100% trigger rate for signal greater than 1/3 photoelectron and a charge measurement up to 30 photoe 5pC) with a linearity of 2%. The gain of each channel can be tuned between 0 and 2 thanks to an 8 bit variable gain preamplifier allowing to compensate the non mity between detector channels. A slow shaper combined with two Sample and Hold capacitors allows storing the charge up to 5pC as well as the baseline In parallel, 64 trigger outputs are obtained thanks to

vo possible trigger pathes : one made of a bipolar or unipolar fast (15 ns) shaper followed by one iscriminator for the photon counting and one made with a bipolar fast shaper (with a lower gain) followed by a discriminator to deliver triggers for larger input charges (> 1pe). The discriminator thresholds are set by two internal 10-bit DACs. A digital charge output is provided by an integrated 8, 10 or 12 bit Wilkinson

#### Contact · Sylvie Blin

#### **SPACIROC**

SPACIROC (Spatial Photomultiplier Array Counting Integrated ReadOut Chip is a 64-channel chip designed to readout negative fast input current pulses such as those provided by Multi Anode Photo Multipliers and for spatial and low power applications. The 64 inputs from MAPMT Anodes are amplified by an 8bit variable gain preamplifier allowing to tune the gain of each channel between 0 and 4 and so to compensate the non-uniformity between detector channels. Each channel provides a 100% tripper rate for signal greater than 1/3 photoelectron. Charge measurements from 2pC up to 220pC are performed using a Time-over-Threshold. A fast Photon Counting (50 MHz) is done thanks to a fast shaper followed by a discriminator, the threshold of which is set by one nternal 10-bit DAC.

The digital part operates continuously and handles data conversion of each Photon Counting and Time-Over-Threshold channel. The digital data are transmitted via dedicated parallel communication links and within the defined Gate Time Unit (GTU). The ASIC data output rate is 40MHz. Spacinoc is radiation

#### Contact : Sylvie Blin SPIROC / EASIROC

hadronic calorimeter using SiPM. This ASIC is due to equip a 10,000-ch demonstrator in 2010. It embeds cutting edge features that fulfil ILC final detector requirements. It has been realized in 0.35 mm SiGe technology.

It has been developed to match the requirements of large dynamic range, low noise, low consumption, high precision and large number of readout channels needed, SPIROC is an auto triggered (down to 50fC), dual gain, 36-channel ASIC which allows to measure on each channel the charge from one photoelectron to 2,000 photoelectron and the time with a Ins accurate Time-to-digital Converter (TDC). An analogue memory array with a depth of 16 for each channel is used to store the time information and the charge measurement, A 12bit Wilkinson Analogue-to-digital Converter (ADC) has bee embedded to digitize the analogue memory content (time and charge on 2 gains).

The data are then stored in a 4 Kbytes RAM. A very complex digital part has been integrated to manage all these features and to transfer the data to the DAO. In parallel, a "spin-off" chip, EASIROC, has been developed. EASIROC, standing for Extended Analogue Si-pm Integrated ReadOut Chip is a 32 channels fully analogue front end ASIC dedicated to readout SiPM detectors.

sed for PERS MuRAY LPARC and medical imaging

Contact : Ludovic Raux

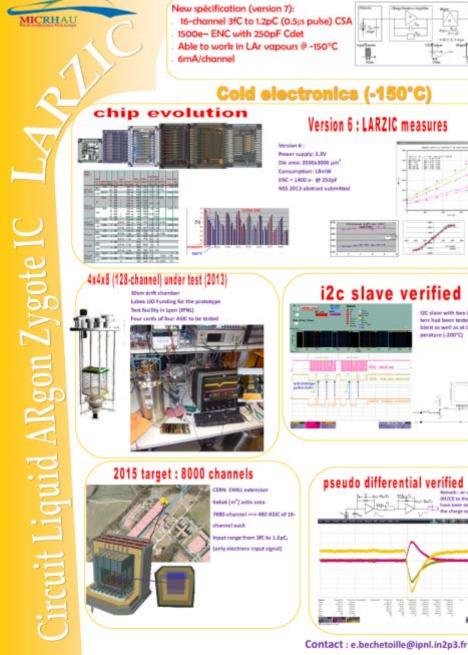

## Electronique à froid

- ☐ Evolution du circuit depuis 2007

- Test à froid de différents blocs

- Ajout de fonctionnalités

- ☐ Test en cours à l'IPNL sur détecteur 128 voies

- 4 cartes de 4 circuits

- Points délicats : filtrage des alimentations

- **Perspectives 2015**

- Test au CERN sur chambre de 6x6x6 [m<sup>3</sup>]

- Dynamique: -3fC à -1.2pC

- ☐ Intégration 16 voies par chip

Ecole de microélectronique de l'IN2P3

Porquerolles -23/27 juin 2013

DC slave with two 8-bit resis ters had been tested at aretient as well as at LN2 terri-Choose | Sanstana

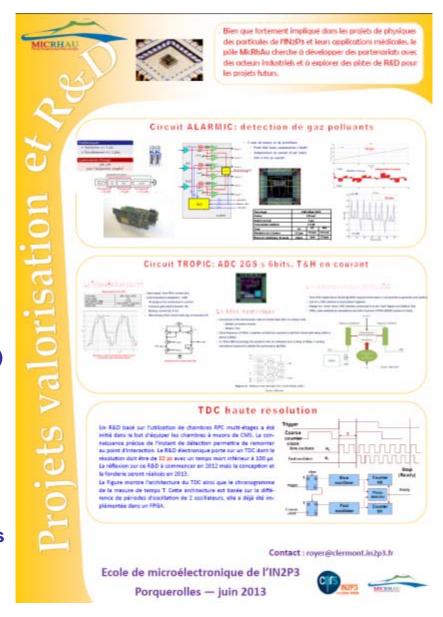

## Projets de valorisation et R&D @ MicRhAu

- □ Projet de valorisation: circuit ALARMIC

- Mesure et surveillance de 3 gaz polluants sans fil

- □ VFE, comparateurs et DAC très basse conso.

- □ R&D: circuit TROPIC

- ☐ T&H et bloc numérique pour ADC 2GHz 6 bits

- □ Application: filtrage optimal temps réel (TEP TOF)

- R&D: TDC haute résolution

- Dédié aux chambres RPC à muons pour CMS

- ☐ Résolution visée: 10 ps

- □ Architecture basée sur la différence de périodes

d'oscillation de 2 oscillateurs

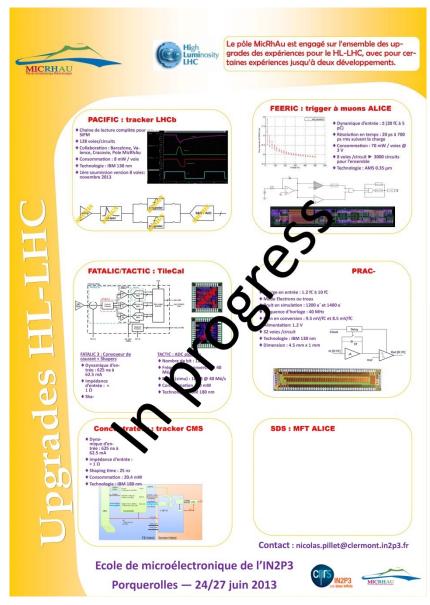

- ☐ Trigger à muons ALICE : circuit FEERIC

- ☐ Front-end analogique / Précision en temps

- ☐ Tracker CMS : circuit PRACTIC 32

- ☐ Front-end analogique multivoie

- ☐ TileCal ATLAS : circuit FATALIC/TACTIC

- ☐ Front-end analogique à sortie numérique

- □ Tracker LHCb : circuit PACIFIC

- □ Front-end analogique multivoie

- □ Tracker CMS : circuit Concentrateur

- Circuit de traitement numérique

- MFT ALICE : circuit SDS

- ☐ Circuit de traitement numérique

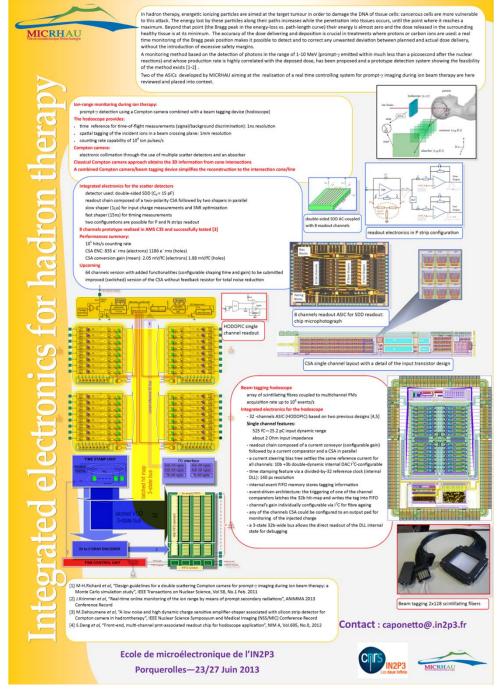

## Electronique intégrée pour applications en hadron thérapie

- □ Aperçu des circuits intégrés réalisés dans le cadre des problématiques de hadron thérapie

- un ASIC multivoie pour la lecture de SDD double polarité a été fondu et testé

- ☐ une deuxième version est prévue

- ☐ un ASIC multivoie mixed-signal pour l'étiquetage temporel et l'enregistrement de la position de hits provenant de fibres scintillantes a été soumis pour la fabrication en Juin 2013

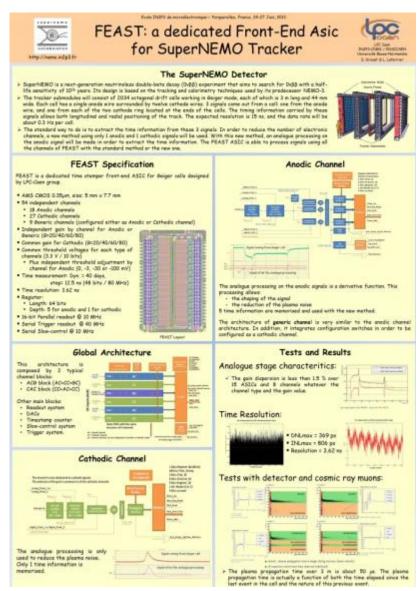

# FEAST: a dedicated Front-End ASIC for SuperNEMO Tracker

#### LPC Caen

- ✓ Service Electronique-Microélectronique

- S. Drouet / L. Leterrier (ASIC)

- F. Boumard / J. Langlois (Cartes de tests)

- ✓ Service Instrumentation

- J. Brégeault (Logiciel d'acquisition)

### SuperNEMO

- ✓ Physique du neutrino (Etude de la double désintégration β sans neutrino)

- ✓ Démonstrateur SuperNEMO

- Construction 2013-2014

- ≈2000 voies pour le tracker (150 ASICs)

#### FEAST

- ✓ Techno: AMS 0,35µm CMOS

- ✓ ASIC pour le trajectographe

- ✓ ASIC codeur de temps avec mise en forme analogique du signal à traiter

- √ 54 voies indépendantes

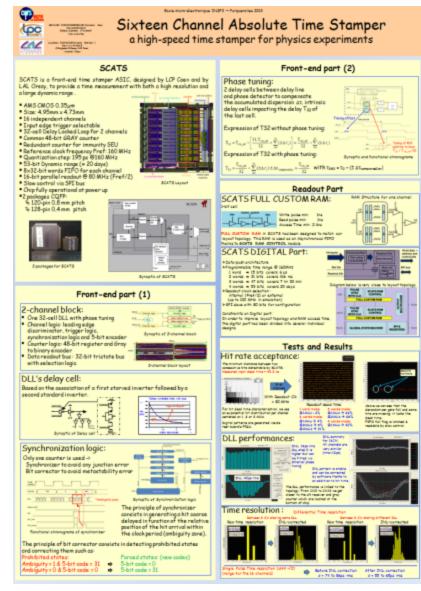

## SCATS

## Sixteen Channel Absolute Time Stamper

## LAL / LPC

C. Beigbeder<sup>1</sup>, D. Breton<sup>1</sup>, S. Drouet<sup>2</sup>, A. El Berni<sup>1</sup>, L. Leterrier<sup>2</sup>, J. Maalmi<sup>1</sup>, V. Tocut<sup>1</sup>, Ph. Vallerand<sup>2\*</sup>

1: LAL Orsay 2: LPC Caen \*: now at GANIL Caen

## SCATS

- Time measurement

- A high-speed, high resolution and large dynamic time stamper

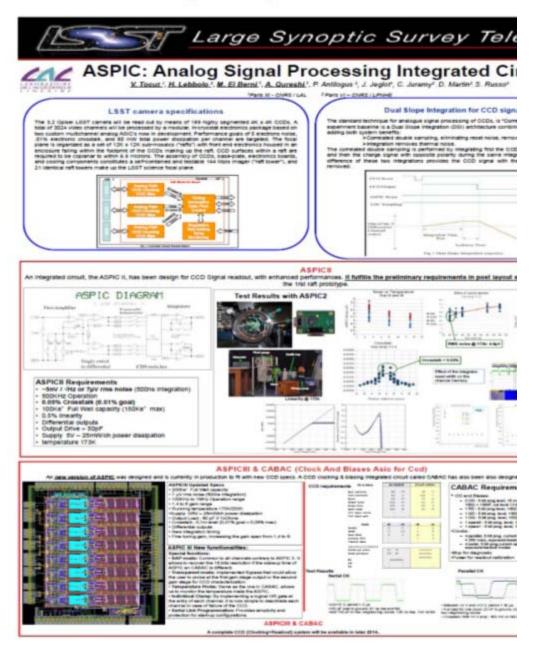

### ASPIC: Analog Signal Processing Integrated Circuit

## LAL/LPNHE – LSST

## Sujet/Domaine

- Energie Noire

- Supernovae

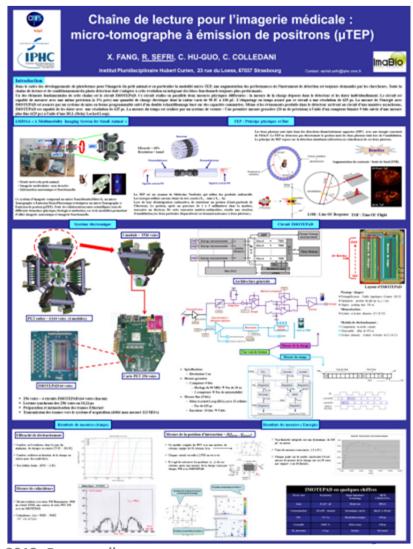

# IMOTEP pour IMagerie TEP

- IPHC Groupe IMABIO

- Plateforme AMISSA

- Sujet/Domaine

- Circuit pour PM multivoies

- Mesure d'énergie corrélée en temps

- Dynamique d'entrée: 2 10<sup>3</sup> à 1%

- Dynamique 10 μs ,résolution 625 ps

- Interlocuteur

- Xiaochao FANG

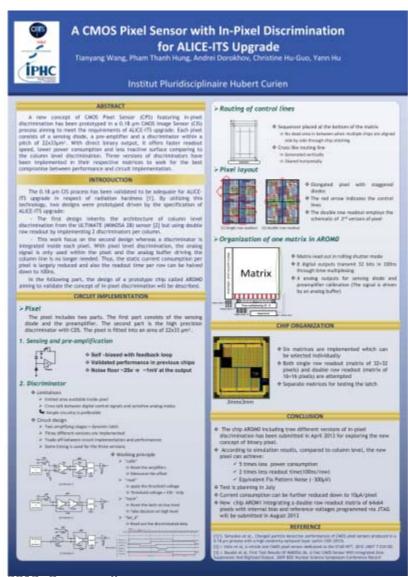

# AROM Accelerated Read Out Mimosa

- IPHC Groupe PICSEL

- Upgrade ITS ALICE

- Sujet/Domaine

- Pixels à discriminateur embarqué

- Faible consommation

- Grande vitesse de lecture

- Etude de 3 architectures

- Interlocuteur

- Hung PHAM

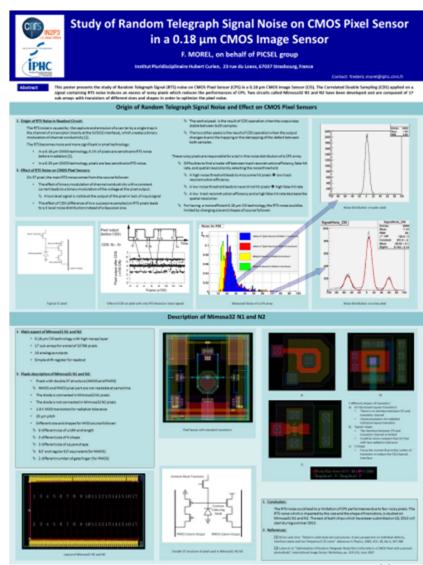

## MIMOSA32 N1 & N2 Etude du bruit "Random Telegraph Signal"

- IPHC Groupe PICSEL

Upgrade ITS ALICE

- Sujet/Domaine

- Optimisation des pixels

- SF pour lecture de la chaîne

- Etude en fonction de la taille et la géométrie du SF

- Interlocuteur

- Frédéric MOREL

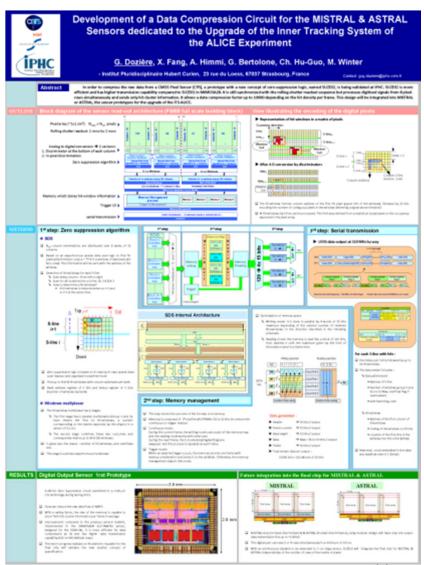

## SUZE02 SUpression de ZEro des capteurs MISTRAL / ASTRAL

- IPHC Groupe PICSEL

- Upgrade ITS ALICE

- Sujet/Domaine

- Suppression de zéros

- Gestion mémoire

- Transmission de données

- Interlocuteur

- Abdelkader HIMMI

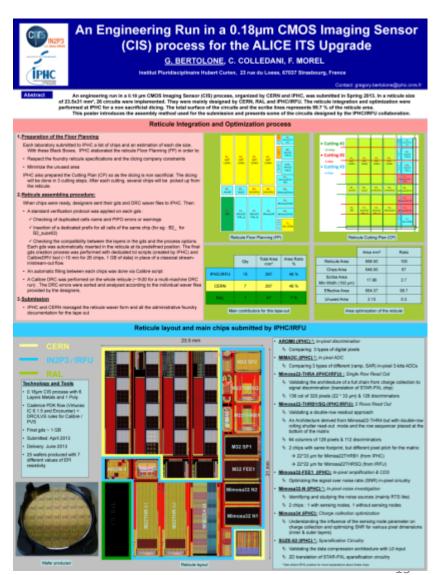

## Réticule ITS1 180 nm Engineering Run

- IPHC Groupe PICSEL

- Upgrade ITS ALICE

- Sujet/Domaine

- Engineering Run / MPW

- Automatisation des procédures d'assemblage de 26 circuits

- Interlocuteur

- Grégory BERTOLONE

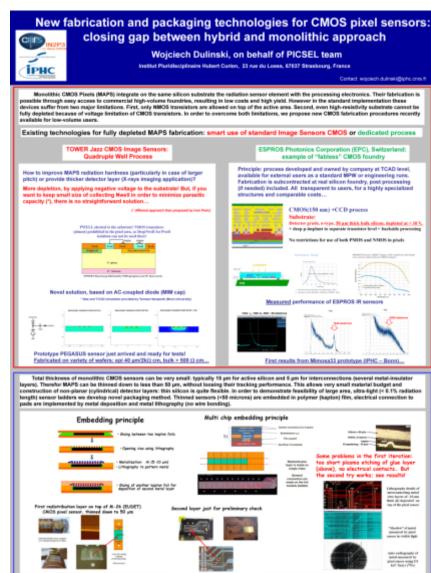

# MIMOSA 34 & CERNWIET Nouveaux procédés de fabrication Monolithique & Hybride

- IPHC Groupe PICSEL

- R&D avancée

- Sujet/Domaine

- CMOS sur substrats HRES

- Capteurs/Flex ultraminces

- Interlocuteur

- Wojciech DULINSKI

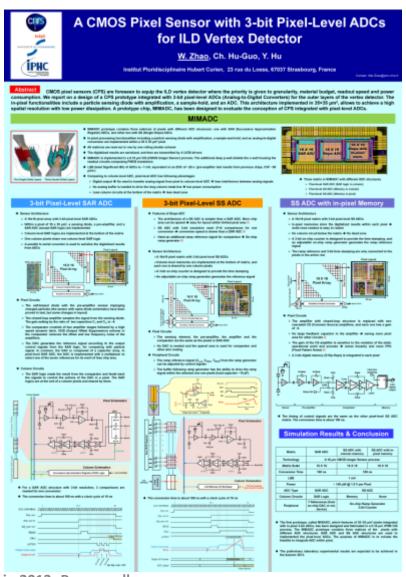

# MIMADC ADC 3 bits intégrés au pixel

- IPHC Groupe PICSEL

- R&D avancée

- Sujet/Domaine

- Pixels à discriminateur embarqué

- Faible consommation

- Grande vitesse de lecture

- Etude de 3 architectures

- Interlocuteur

- Yang ZHOU

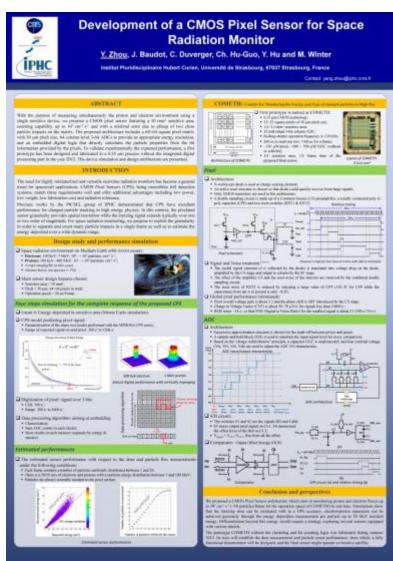

#### **COMETH**

# COunter for Monitoring the Energy and Type of charged particles in High flux

- IPHC Groupe PICSEL

- Space Radiation Monitoring

- Sujet/Domaine

- Dosimetry

- High flux environment

- Interlocuteur

- Yang ZHOU

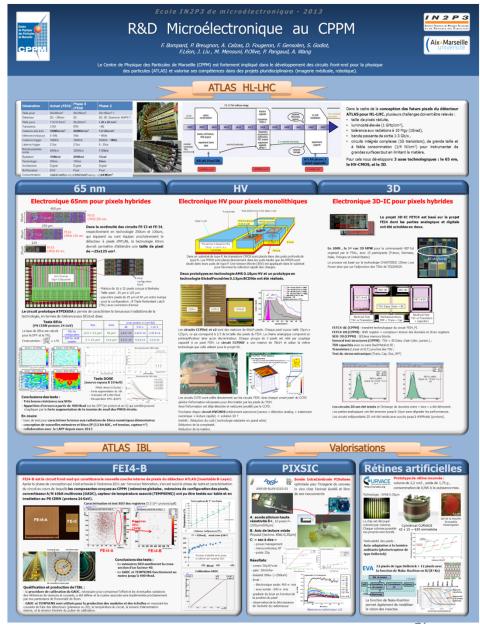

### R&D microélectronique au CPPM

### **CPPM**

Equipe microélectronique (conception - mesure - test)

- ATLAS / LHC et HL-LHC

- IBL (phase 0)

- circuit FEI4

- phase 1 et 2

- Solution en 65nm

- Solution en techno 3D

- Solution en HV CMOS

- Imagerie

- Rétine artificielle

- Sonde intracérébrale

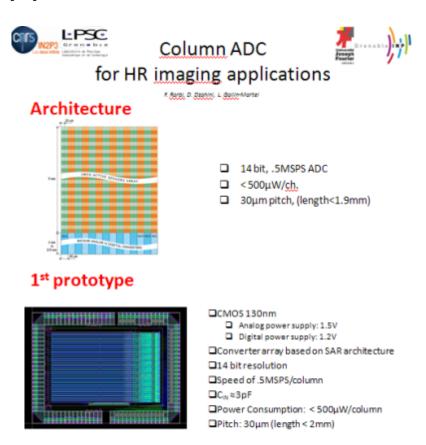

# Column ADC for HR imaging applications

LPSC Grenoble – Gravit

Massive Array ADC

- Interlocuteur

- Fatah RARBI

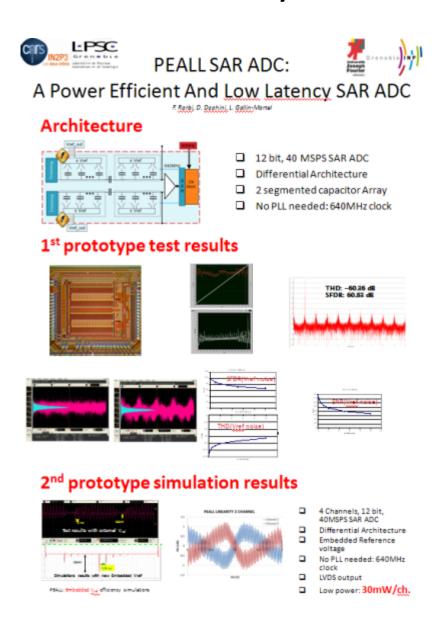

## PEALL 12-b, 40-MSPS SAR ADC:

## IN2P3 Les deux infinis A Power Efficient and Low Latency SAR ADC

- LPSC Grenoble

- ATLAS

- High-speed and low power ADC

- Interlocuteur

- Fatah RARBI

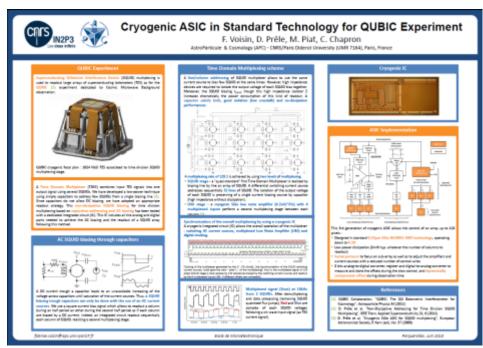

# Cryogenic ASIC in Standard Technology for QUBIC Experiment

- AstroParticule & Cosmologie (APC)

F. Voisin, D. Prêle

- Description de l'ASIC réalisé pour l'instrument QUBIC dédié à l'observation du fond diffus cosmologique