# Ecole Microélectronique 2015 Fréjus – Villa Clythia 17 mai -22 mai 2015

## Thèmes de cette Ecole 2015 :

- > Le futur de la microélectronique :

- Up-grade LHC,

- Process 65 nm,

- Etude de blocs en 65 nm,

- La microélectronique à l'IN2P3/IRFU (table ronde)

- ➤ La micro-cryo-électronique

- Les ADC SAR

- Le High Speed

- Les cellules numériques

- > Les outils

#### Ecole de Microélectronique IN2P3 2015 - 17 mai au 22 mai - Fréjus

### Dimanche 17 mai : arrivée des participants

|                 |                       | zon : Diner                                                                                       |                                                             |  |  |  |

|-----------------|-----------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| Lundi 18 mai    | 08:15                 | Présentation de l'école                                                                           | Gisèle Martin-Chassard<br>(OMEGA)<br>Hervé Mathez<br>(IPNL) |  |  |  |

|                 | 08:30<br>10:00        | Evolution de la microélectronique                                                                 | Alessandro Marchioro (CERN)                                 |  |  |  |

|                 |                       | Café                                                                                              |                                                             |  |  |  |

|                 | 10:30                 | Upgrade HL-LHC                                                                                    | Philippe Farthouat (CERN)                                   |  |  |  |

|                 | 12:00                 |                                                                                                   | · · · · · · · · · · · · · · · · · · ·                       |  |  |  |

|                 | 12:15                 | Déjeuner                                                                                          |                                                             |  |  |  |

|                 | 16:00<br>17:30        | Revue de la technonogie 65nm et des blocs développés                                              | Valerio Re (INFN)                                           |  |  |  |

|                 | 18:00                 | Café                                                                                              | Marking Market (CDDM)                                       |  |  |  |

|                 | 18:00                 | Retour d'expérience en technologie 65 nm dans le cadre de ATLAS/LHC                               | Moshine Menoumi (CPPM)                                      |  |  |  |

|                 | 19:30                 | Posters Building blocks Remarques : Les posters doivent être techniques et présenter un bloc d'un | Tous                                                        |  |  |  |

|                 | 20:00                 | Diner                                                                                             | <u> </u>                                                    |  |  |  |

|                 | 20.00                 | Differ                                                                                            |                                                             |  |  |  |

|                 | 08:30                 |                                                                                                   | 1                                                           |  |  |  |

|                 | 10:00                 | Etude de cellules analogiques en technologie fines  Café                                          | Jacques Lecoq (LPC Clerm)                                   |  |  |  |

|                 | 10:30                 | Etude de cellules analogiques en technologie fines (suite)                                        |                                                             |  |  |  |

|                 | 11:15                 | Discussion                                                                                        | Jacques Lecoq (LPC Clerm)                                   |  |  |  |

| ai              | 11:30                 |                                                                                                   | +                                                           |  |  |  |

| E 6             | 12:00                 | Front-end at cryogenic temperature                                                                | Edouard Bechetoille (IPNL)                                  |  |  |  |

| Ξ               | 12:15                 | Déjeuner                                                                                          |                                                             |  |  |  |

| Mardi 19 mai    | 16:00                 |                                                                                                   | 01. 1. 0. 11. 1 (151.10)                                    |  |  |  |

|                 | 17:30                 | La microélectronique à l'IN2P3/IRFU                                                               | Claude Colledani (IPHC)                                     |  |  |  |

|                 |                       | Café                                                                                              |                                                             |  |  |  |

|                 | 18:00                 | Table ronde : Evolution de l'électronique à l'IN2P3                                               | Catherine Clerc (IN2P3)                                     |  |  |  |

|                 | 19:30                 | Table folide . Evolution de relectionique à finze 3                                               | Catheline Clerc (INZF3)                                     |  |  |  |

|                 | 20:00                 | Diner                                                                                             |                                                             |  |  |  |

|                 |                       |                                                                                                   |                                                             |  |  |  |

|                 | 08:30                 | SAR ADC design and calibration techniques                                                         | Pr Yun Chiu                                                 |  |  |  |

|                 | 10:00                 | · · · · · · · · · · · · · · · · · · ·                                                             | (Univ.Dallas-Texas)                                         |  |  |  |

| _               | 40.00                 | Café                                                                                              | 5 V 0                                                       |  |  |  |

| nai             | 10:30                 | SAR ADC design and calibration techniques                                                         | Pr Yun Chiu                                                 |  |  |  |

| 2               | 12:00                 | D.::                                                                                              | (Univ.Dallas-Texas)                                         |  |  |  |

| Mercredi 20 mai | <b>12:15</b><br>16:00 | Déjeuner                                                                                          | Pr Yun Chiu                                                 |  |  |  |

|                 | 17:30                 | SAR ADC design and calibration techniques                                                         | (Univ.Dallas-Texas)                                         |  |  |  |

|                 | 17.30                 | Café                                                                                              | (Ulliv.Dallas-Texas)                                        |  |  |  |

|                 | 18:00                 |                                                                                                   |                                                             |  |  |  |

|                 | 19:30                 | Méthodologie de caractérisation des cellules numériques                                           | Xavier Llopart (CERN)                                       |  |  |  |

|                 | 20:00                 | Diner                                                                                             |                                                             |  |  |  |

|                 |                       |                                                                                                   |                                                             |  |  |  |

|                 | 08:30                 | A                                                                                                 | D. L. ( D (255:::                                           |  |  |  |

| Ji 21 mai       | 10:00                 | Aspects on high speed and radiation tolerance I/O                                                 | Roberto Beccherle (CERN)                                    |  |  |  |

|                 |                       | Café                                                                                              |                                                             |  |  |  |

|                 | 10:30<br>12:00        | Aspects on high speed and radiation tolerance I/O                                                 | Roberto Beccherle (CERN)                                    |  |  |  |

|                 | 12:15                 | Déjeuner                                                                                          |                                                             |  |  |  |

|                 | 16:00                 |                                                                                                   | Domion Prâlo (ABC)                                          |  |  |  |

|                 | 17:30                 | Front-end & Multiplexage at cryogenic temperature                                                 | Damien Prêle (APC)                                          |  |  |  |

| =               |                       | Café                                                                                              |                                                             |  |  |  |

| endi 2          |                       |                                                                                                   | 1                                                           |  |  |  |

| Jeudi 21        | 18:00                 | Outile CAO : PVS Voltue Tempus                                                                    | Frédéric Moral (IDUC)                                       |  |  |  |

| Jeudi 2         | 19:30                 | Outils CAO : PVS Voltus Tempus                                                                    | Frédéric Morel (IPHC)                                       |  |  |  |

| Jendi 2         | 19:30<br>19:30        |                                                                                                   |                                                             |  |  |  |

| Jeudi 2         | 19:30                 | Outils CAO : PVS Voltus Tempus  Bilan de la formation  Diner                                      | Frédéric Morel (IPHC)  Tous                                 |  |  |  |

Vendredi 22 mai : Départ des participants

Pour les pauses

COPIL du réseau Microélectronique

Remplir le questionnaire de fin d'école

Session Posters Fréjus – Villa Clythia 17 mai -22 mai 2015

## LPSC Grenoble

- 1) Very High speed redundant SAR ADC, designed for ATLAS

- 2) High resolution column ADC for CMOS Image sensors

Daniel Dzahini, Fatah Rarbi, Mohamed Zeloufi

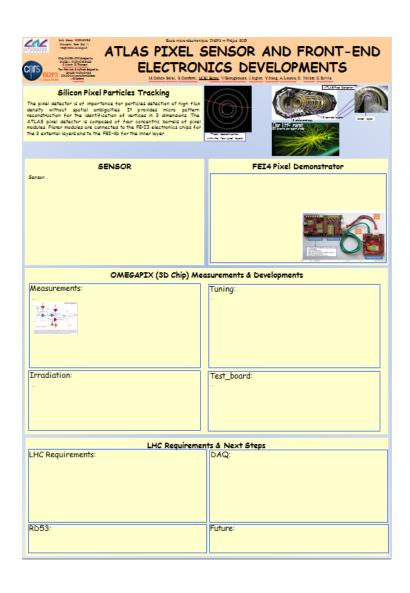

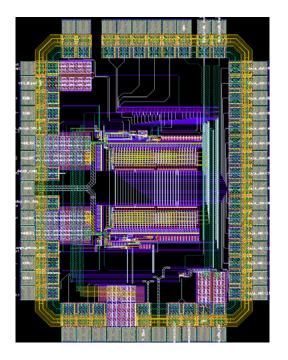

# ATLAS PIXEL SENSOR AND FRONT-END ELECTRONICS DEVELOPMENTS

## LAL ATLAS Pixel

M. Cohen Solal, S. Conforti, <u>M. El Berni</u>, V.Gkougkousis, J.Jeglot, Y.Jiang, A.Lounis, C. Nellist, C.Sylvia

- Chip Omegapix2 designed by OMEGA (G.Martin-Chassard, D.Thienpont)

- Test Firmware and Software designed by LPNHE (O. Le Dortz)

Design de mémoires de configuration tolérantes au Single Event Upset pour le futur circuit de lecture des pixels de ATLAS

Techno: TSMC 65nm

Denis Fougeron, Mohsine Menouni, Patrick Pangaud, Anging Wang

Building blocks en technologie X-FAB SOI 180nm Jean-Baptiste Cizel : Weeroc/LLR

SPACIROC: chip spatial de lecture MAPMT Sylvie Blin, Damien Thienpont CITIROC: chip de lecture de SIPM Stephane Callier, Ludovic Raux techno: AMS SiGe 350nm

"Intégration « rad-hard » d'un protocole I2C en BiCMOS 0,35µm AMS".

C. Beillimaz, D. Prêle et F. Voisin

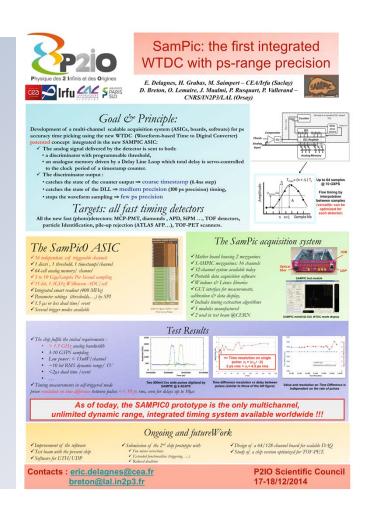

# SamPic: le premier WTDC intégré pour la mesure à la pico-seconde. (Olivier Gevin)

Développement d'un système multi-canal pour la mesure du temps à la pico-seconde en utilisant la technique (brevetée) du WTDC intégrée dans la puce SAMPIC en technologie AMS 0,18µm.

Le principe consiste à intégrer trois niveaux de précision de la mesure du temps:

- Un compteur.

- Une DLL.

- Une analyse de la forme de l'impulsion (WTDC).

Le chip intègre, dans chaque canal une DLL de 64 cellules, et chaque cellule est codée par un ADC 11 bits.

$\Rightarrow$ 1024 ADC dans le chip.

Un système de test pour 32 canaux a été développé et les tests font état d'une résolution en temps de 5ps.

## ADC 13-bit 32 voies pour applications spatiales

CEA, IRFU F-91191 Gif sur Yvette Cedex, Florent Bouyjou

Présentation d'un ADC 32 voies, 13-bit, 2,56 µs de temps de conversion, 2V de plage d'entrée appélé OWB-1. L'architecture est basée sur une architecture de type Wilkinson à base de DLL. La technologie utilisée est la CMOS 0,35 µm d'AMS.

### Performances mesurées :

| Nb voies               | 32 //                                                                          |

|------------------------|--------------------------------------------------------------------------------|

| Bits                   | 13 bit                                                                         |

| Plage d'entrée         | 2 V                                                                            |

| Temps de conversion    | 2,56 $\mu$ s (2,7 $\mu$ s de temps d'échantillonnage)                          |

| LSB                    | 244 μV (DLL: 312,5 ps)                                                         |

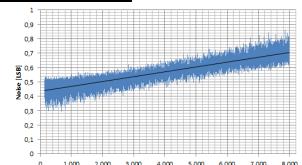

| Bruit RMS              | [0,29 à 0,87 L5B] : 71 à 212 μV rms                                            |

| NLD                    | +0,31 à -0,28 LSB                                                              |

| NLI                    | +2,1 à -1,3 LSB                                                                |

| Puissance/canal        | 0,8 mW en statique et dynamique par voie<br>TOTAL : 57mW                       |

| Fréquence<br>d'horloge | 1 MHz LVDS en entrée d'ASIC<br>100 MHz en sortie de PLL<br>3,2 GHz pour la DLL |

| Température            | -40 à 40 °C                                                                    |

| Layout                 | 50 * 2000 μm par voie : TOTAL 18 mm²                                           |

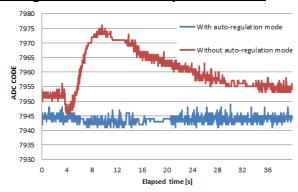

Un système d'autocompensation en température est aussi intégé et permet de compenser les effets de la température entre  $-40^{\circ}C$  et  $+40^{\circ}C$ .

Des techniques de dessin du layout sont utilisées afin d'augmenter la tolérence de l'ASIC aux Single Event Latchup (SEL)

### Mesure du bruit :

### Autorégulation en température

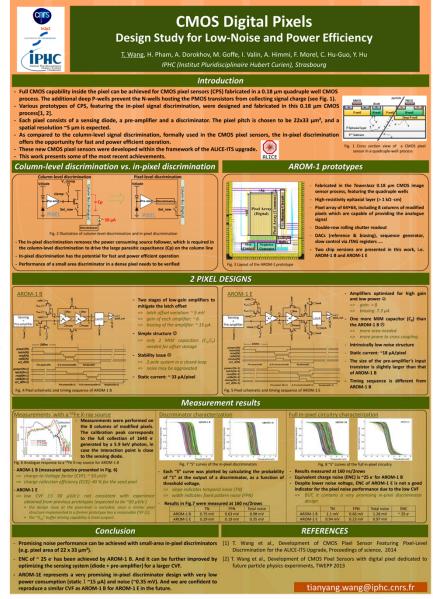

# IPHC:CMOS Digital Pixels Design Study for Low-Noise and Power Efficiency

- Presented by WANG Tianyang,

- PhD student

- Context: ALICE ITS upgrade

- Building Block: Digital pixel

- Allow for low power and high speed

- Main Constraint

- Small area (22 × 33  $\mu$ m<sup>2</sup>) & Low Noise

- Two AROM-1 prototypes presented

- AROM-1 B

- Static current: ~ 33 μA/pixel

- In-pixel discriminator noise: ~ 0.98 mV

- ENC: ~ 25 e<sup>-</sup>

- AROM-1 E

- Static current: ~ 18 μA/pixel

- In-pixel discriminator noise : ~ 0.35 mV

- Promising in-pixel discriminator design

# Poster: Interpolateur de temps à haute résolution (50ps)

Dans le cadre d'une R&D sur le codage en temps, le LPC Caen a développé un interpolateur de temps haute résolution comportant 2 voies. Ce interpolateur est basé sur une boucle à verrouillage de retard (DLL) et une ligne à retard contrôlée par un deuxième DLL verrouillé sur la première.

Cette architecture a été optimisée dans le but d'éviter la mise en œuvre d'un système d'étalonnage compliqué.

Ce bloc de base a été conçu pour fournir une mesure de l'intervalle de temps entre le signal d'horloge (Fin=160MHz) et le signal de « hit » entrant sur la voie.

La taille minimum de cet intervalle de temps correspond de la période d'horloge divisée par 128 (environ 50 ps) et la résolution de temps est d'environ 40 ps RMS.

Le signal d'horloge est commun aux deux voies et une mesure différentielle (temps de vol) peut être faite avec une résolution de temps d'environ 60 ps RMS.

Les données temporelles sont disponibles par l'intermédiaire d'un bus de données 16 bits.

Contact : Laurent LETERRIER Email: leterrier@lpccaen.in2p3.fr

Présentation Activités SEM 13

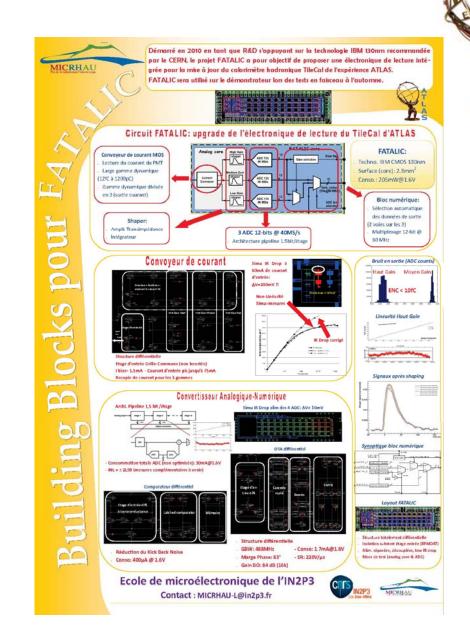

"Buildings blocks for FATALIC Asic"

ATLAS upgrade

Contact : L.Royer MICRHAU-L@in2p3.fr