#### Conception de cellules analogiques En technologies 350, 180, 2x130 et 65 nm

Conditions:

Signaux référencés à Vcc/2 Amplitude +-0.5 V

Fréquence de base 40 MHz

#### A quoi s'attendre

« Les technologies fines sont très avantageuses pour les circuits digitaux, Au détriments de la conception des circuits analogiques. »(cf. cours Pastre 2013)

Vcc diminue ...

Gm/Gds diminue ...

Vearly diminue ...

Vth reste constant ou augmente, de fait se rapproche de Vcc/2. Et devient moins élevée pour les Pmos.

Vcc/Vth diminue

Effet de substrat augmente au moins relativement/Vcc

La bande passante ... augmente en digital, ... mais en analogique?

Gm/gds=(Gm/Id)(Id/Gds)=(Gm/Id)Vearly

Jacques Lecoq Ecole in2p3 2015 FREJUS

Amplificateurs à (très) grands gains

Comparateurs asynchrones optimalisés en produits gain bande

Comparateurs synchrones optimalisés en sensibilité et kick back noise.

Switches de qualité.

## Amplificateurs

- Grands gains ( $10^4$  à  $10^5$  ou plus)

- Dynamique >= 1V (+- 0.5 en diff.)

- · Prévus pour des ADC 40 Ms ou plus

- Stables en gain 2

- 12 à 15 bits

- · Pas de tensions auxiliaires.

- Méthode de dimensionnement simple, efficace (et indépendante de la techno).

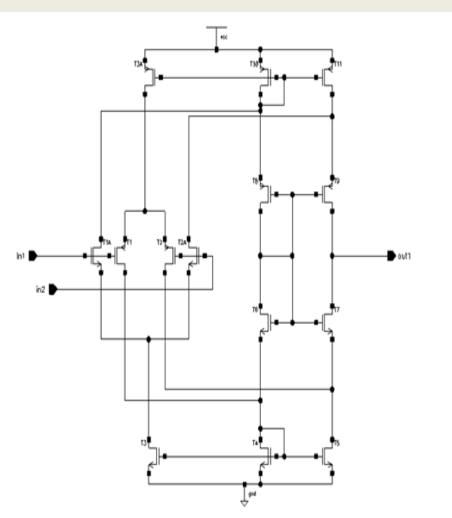

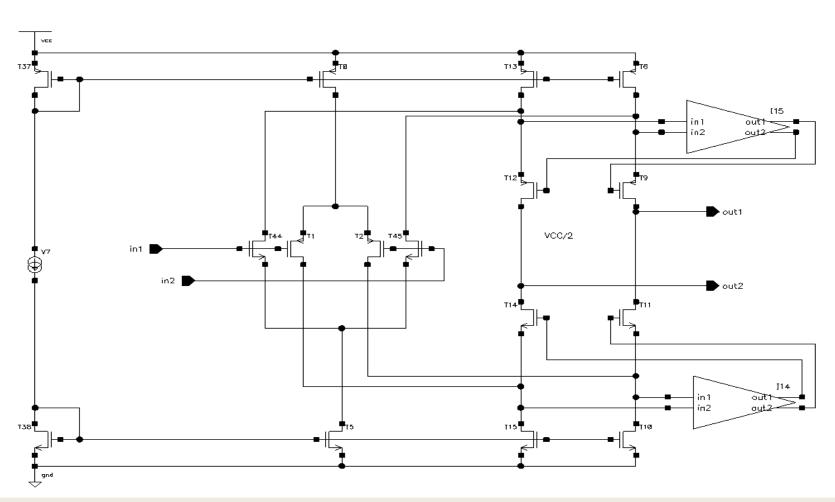

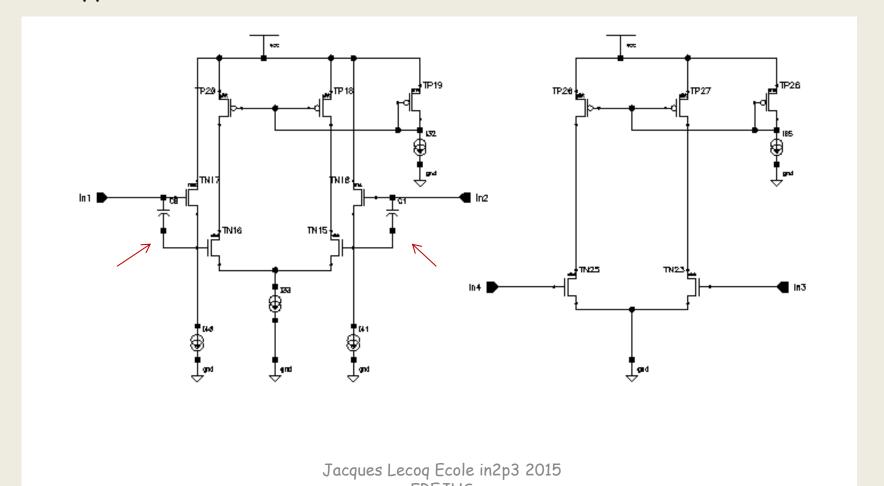

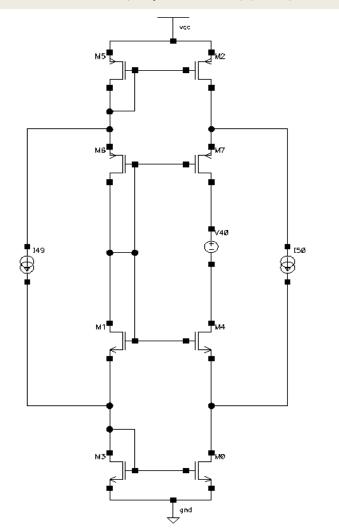

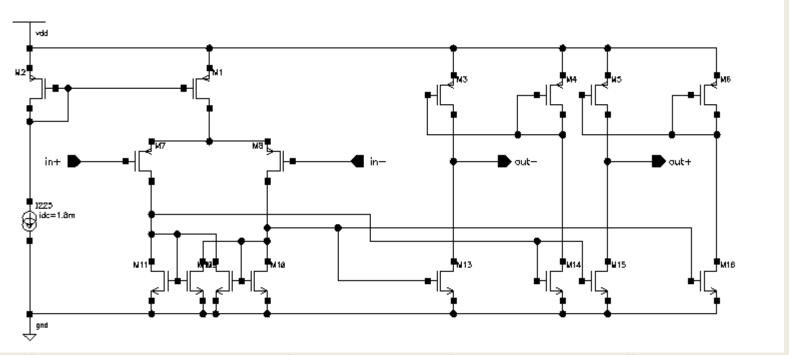

## Schéma de départ

Publication de 1997 .... En 1.6µ

Auto polarisé. Symétrique

Double cascode replié.

Les branches de sortie sont

Constituées de 4 diodes/charges

Actives. Les courants sont tous des

Recopies des courants des diodes.

D'où le dimensionnement:

On se fixe le courant.

On cherche les W/L donnant cette

Valeur de courant, et le facteur K

Entre les N et les P pour que la

sortie (MC) soit au point milieu.

## Schéma de départ

En AMS 350 nm:

Courant:  $300 \mu A$ .

Tension d'entrée (MC.): Vcc/2

Tension sortie; Vcc/2 Transistors en région 2

Vcc/Vth de 6 à 4.4 Effet substrat max 250mV

Gain obtenu 3000 à 6000 Bande passante 1 GHz Produit gain bande 4.5 GHz En diminuant le courant, on peut atteindre des gains de 70000!

Grand confort!

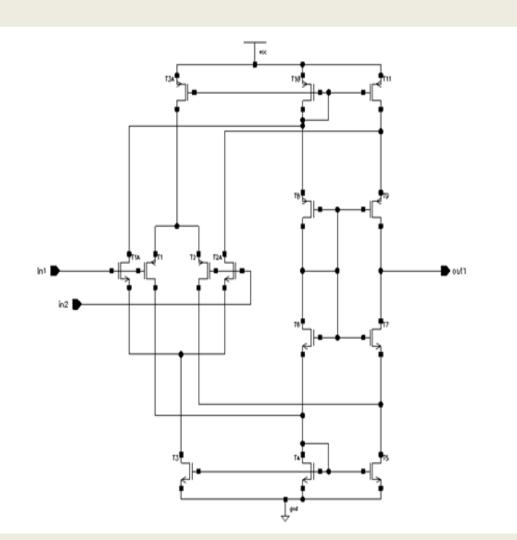

#### Le passage en différentiel est immédiat Une CMFB est nécessaire

#### Dimensionnement Slew rate

Les courants sont donnés par le slew rate

Ici le courant disponible en sortie donc dans T(7) (8) est donné par la différence entre I dans T(2) (5) et I dans T(3) (6)

I(3) est fixe. Le slew rate est donné par L'entrée « si la différence est possible » Donc si I(3)  $\rightarrow$  I(2).

Sinon le slew rate est plus faible, au premier ordre donné par I(3).

Si I(3) nettement trop faible I(2) change de région => petit dysfonctionnement.

Optimal I(2)=I(3) d'où I(7)=I(2)/2

T1=T2=T3=KT4,5,6=2T7=2KT8

Pour T(entrée) soit K soit gm

#### Il faut plus de gain: Boost des cascodes

## Il faut plus de gain: Boosts des cascodes effets avec des boosts idéaux

#### Exemple:

Pour un gain de 665 sans boost:

On Obtient

1360 avec des boosts de gain2 12500 avec des boosts de gain 20 120000 avec des boosts de gain 200

1200000 avec des boosts de gain 2000

Pour une technologie donnée L'ordre de grandeur de la limite est Donné par le carré du gain sans boost

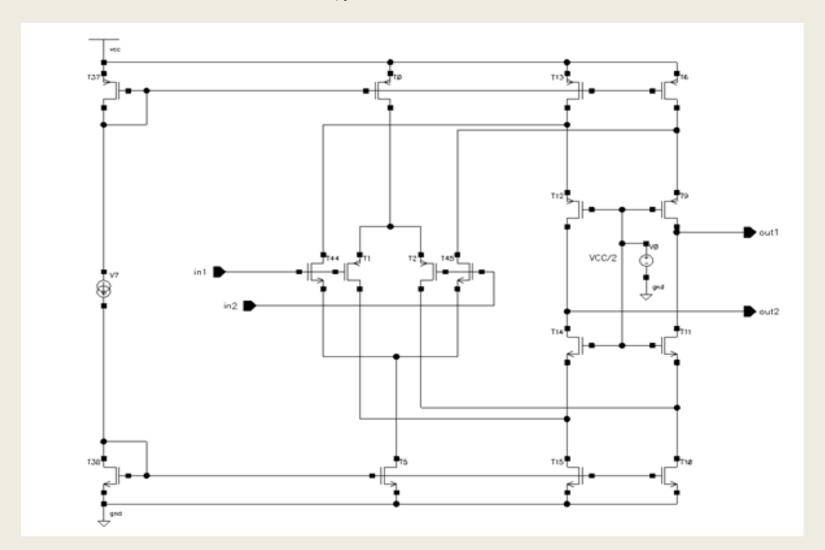

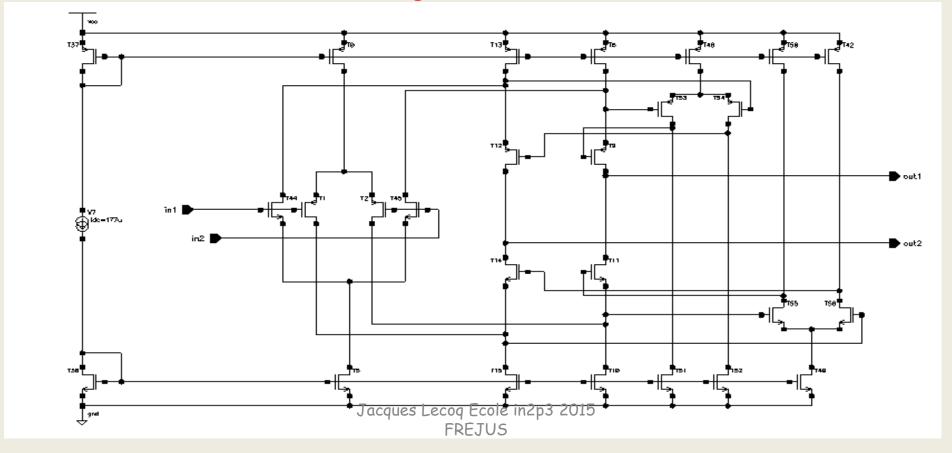

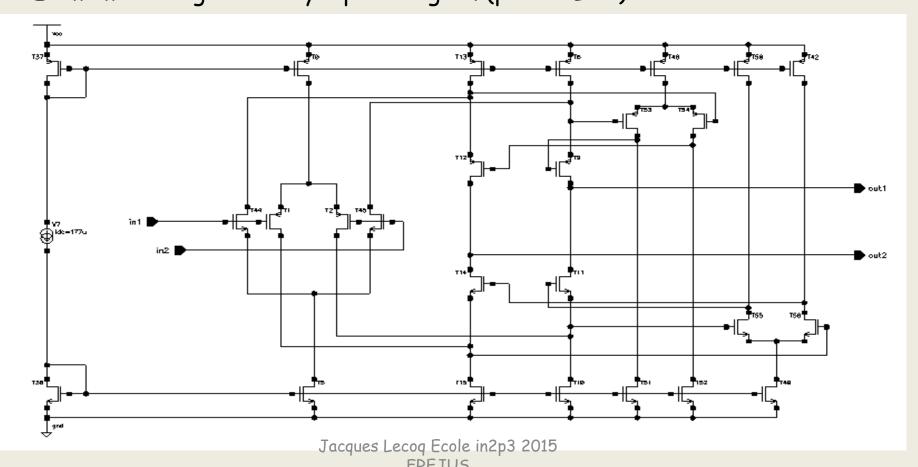

# Application : les boosts sont de simples paires différentielles

Exemple en AMS 0.35  $\mu$ , alimentation 3.3V , courant de 300  $\mu$ A. Gain de 300 000, 2 V diff. de dynamique (grand confort!) Seul petit point faible, le produit gain bande n'est « que » de 4.5 GHz On peut améliorer la bande passante au détriment du gain.

Tous les transistors sont en région 2

#### Portage en AMS 180 nm

Alimentation 1.8 V, courant 300  $\mu$ A Problème de point de fonctionnement des paires différentielles. 1.43 V pour la paire P, 380 mV pour la N c'est très en dessous des seuils élevés pour cette technologie. (Vcc/Vth = 3.6) Et même en région 3 il n'y a plus de gain. (pas de LVT)

#### Portage en AMS 180 nm

Problème des paires différentielles, deux solutions:

- Intercaler un suiveur. Avantage: facile, une seule paire à étudier Inconvénient consomme plus, capacité d'accélération!

- Supprimer la source de courant.

#### Portage en AMS 180 nm

Résultats des deux portages:

Avec les suiveurs, il faut quasiment 1 pF pour rétablir la stabilité. On obtient un gain de 100K et un produit gain bande de 8 GHz

Avec la liaison directe sans source de courant, le schéma est plus simple La consommation plus faible.

Le gain obtenu est de 95 K, le produit gain bande de 7.75 GHz MAIS, dans les deux cas:

Les transistors des paires différentielles sont en région 3 (VGS en dessous de seuil)

L'ordre de grandeur des tensions de seuil est : 0.5 V pour les N et 0.430 pour les P

Vcc/Vth = 3.6 à 4.2

La paire différentielle P a nettement moins de gain que la N.

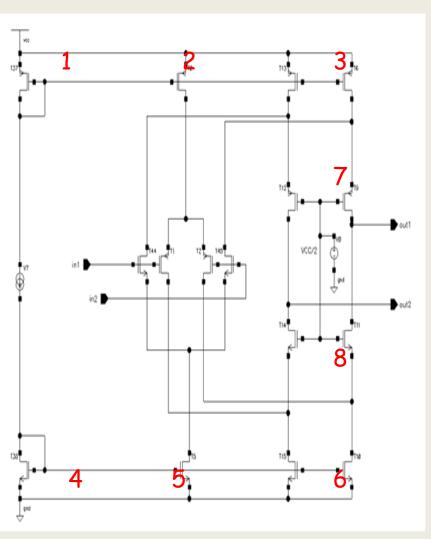

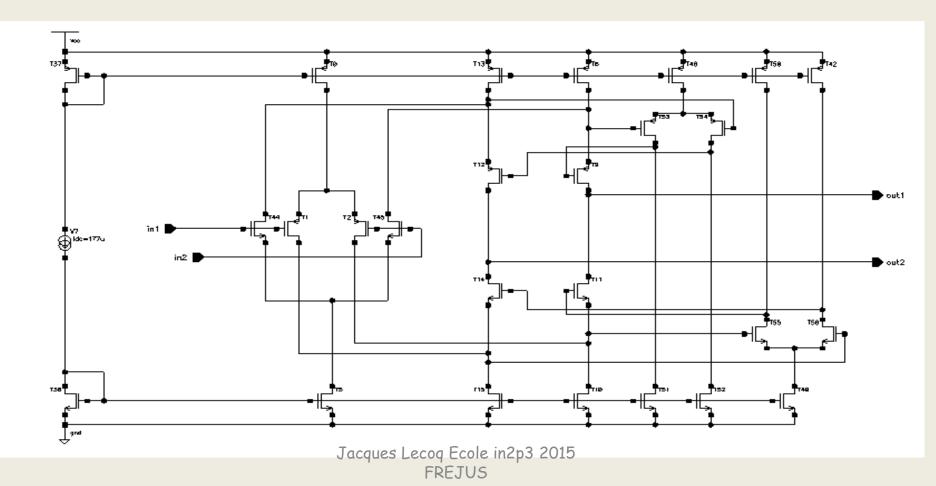

#### Portage en IBM 130 nm

Pour les paires différentielles on est sauvé par les LVT. Alimentation est 1.6 V, courant 350  $\mu$ A Le gain « chute à 30000 » du fait du gm/gds qui est moins bon. mais le produit gain bande est de 26 GHz.

#### Plus de gain: plus de gain dans les boosts

Avec des cascodes dans les boosts et le même courant Le gain monte à 110 000 Le produit gain bande est le même (26 G)

#### Gain 110 000 optimalisé pour ADC

Courant: 350  $\mu$ A en entrée. Un peu de triche: 250 $\mu$ A en sortie au lieu de 350

Le gain est de 110 000 mais surtout, il ne descend pas en dessous de 83000 A pleine échelle.

Sur le banc de test de Laurent on mesure:

Consommation 1.68 mA (dont 350  $\mu$ A du maitre de courant)

Gain de 2=2 (en fait 1,999939)

Produit gain bande sur 2.4 pF: 547.9 M

Marge de phase ampli. 79,43

Marge de phase boost 1: 60,11

Marge de phase boost 2: 62.16

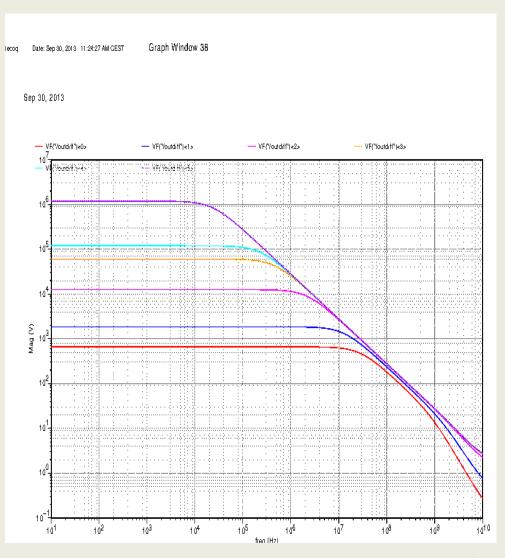

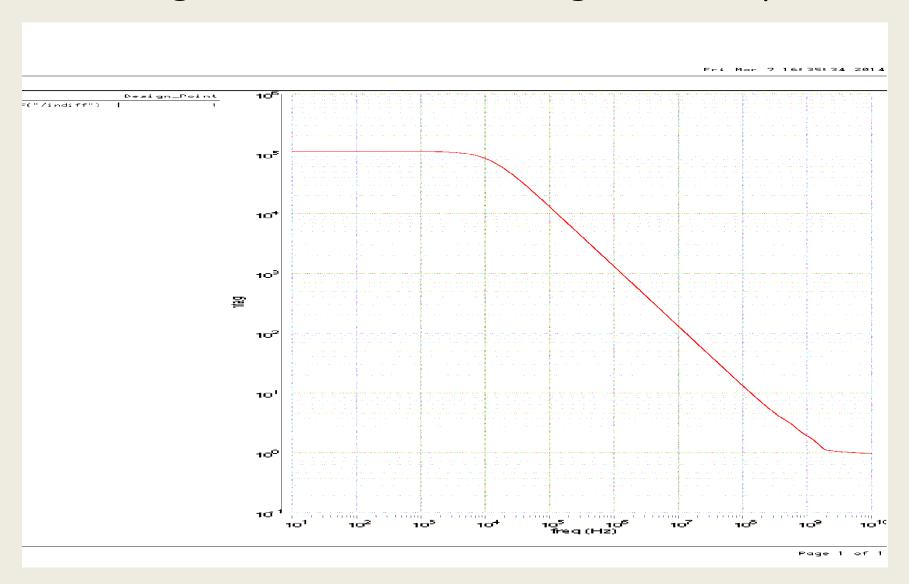

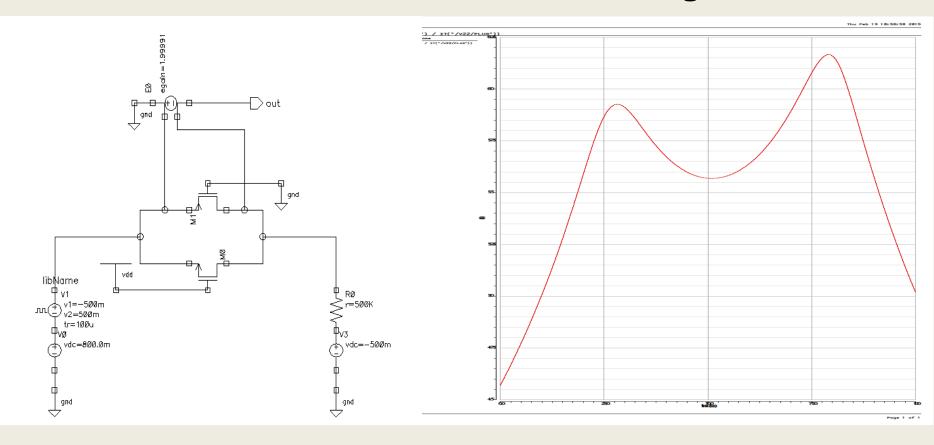

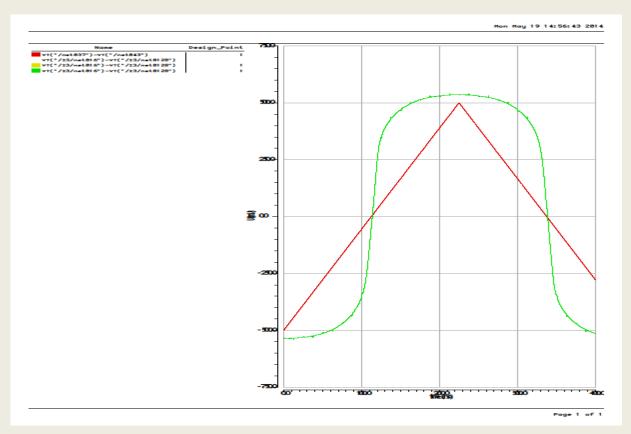

#### Diagramme de Bode, chargé sur 2.6 pF

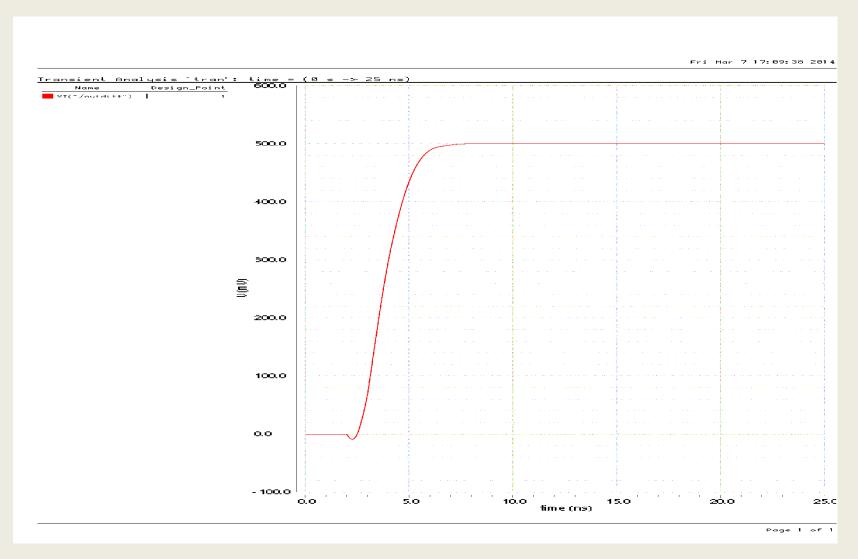

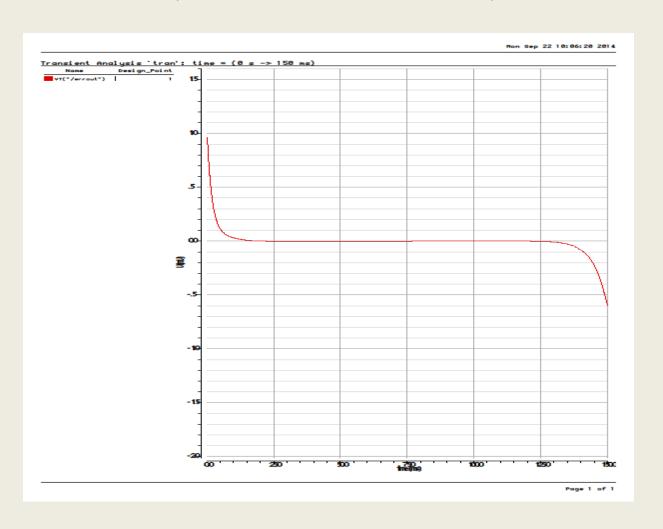

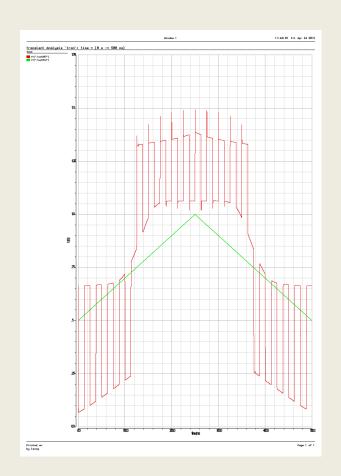

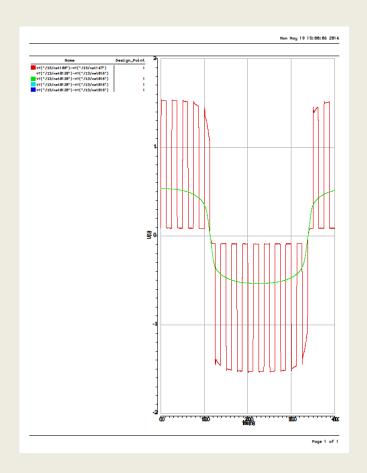

# Gain 110 000 optimalisé pour ADC réponse en transitoire

# Gain 110 000 optimalisé pour ADC linéarité au gain2 sur 1.5 V

#### Pour un ADC de 14-15 bits Il faut charger sur 10 pF!!!!!

Avec exactement le même schéma en multipliant tout par 4 (courant et tailles des transistor):

On obtient, sans grande difficulté:

Un gain de 140 000 qui ne descend pas en dessous de 120 000 à pleine échelle.

Un produit gain bande de 25 G.

Un temps d'établissement à la précision de 14 bits, chargé sur deux fois 9 pF de 6.8 ns.

Sur le banc de test « Laurent modifié 14 bits » tout est OK.

### Résultats:

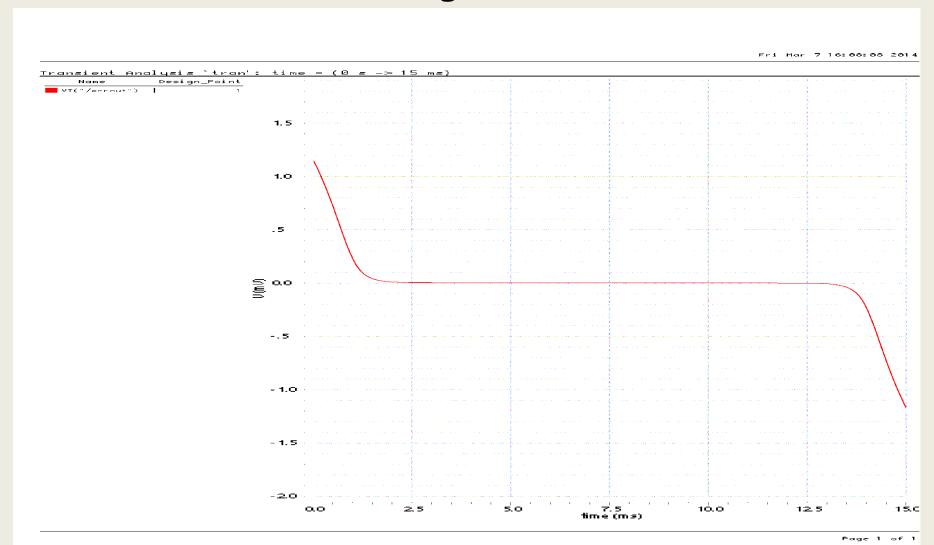

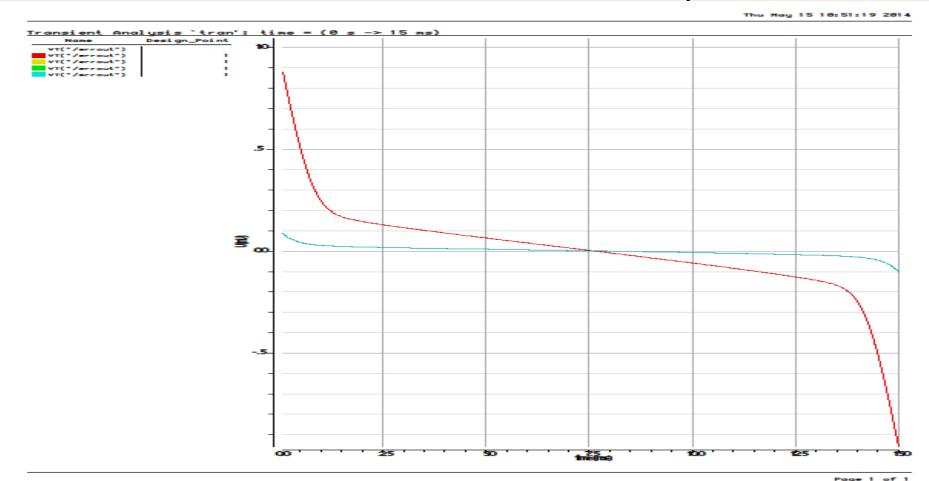

# Erreur au gain 2 sur 1.5V: En rouge pour l'ampli de 20K, en bleu celui de 140K. L'erreur reste inférieure à 10 $\mu$ V pour 1V.

#### Portage en IBM 130 nm

La facteur qualité Gm/Gds est moins bon qu'en 180 nm MAIS: Le rapport Vcc/Vth est bien meilleur, surtout avec les LVT qui sont très bons.

Vth= 290 à 330 mV pour N, 310 à 360 pour les P Vth= 220 mV pour les LVT N comme pour les P.

Soit Vcc/Vth de l'ordre de 5 et Vcc/Vth de l'ordre de 7.3 pour les LVT

Du coup on peut utiliser des transistors plus petits

Le gain est un peu moins bon mais le produit gain bande est excellent.

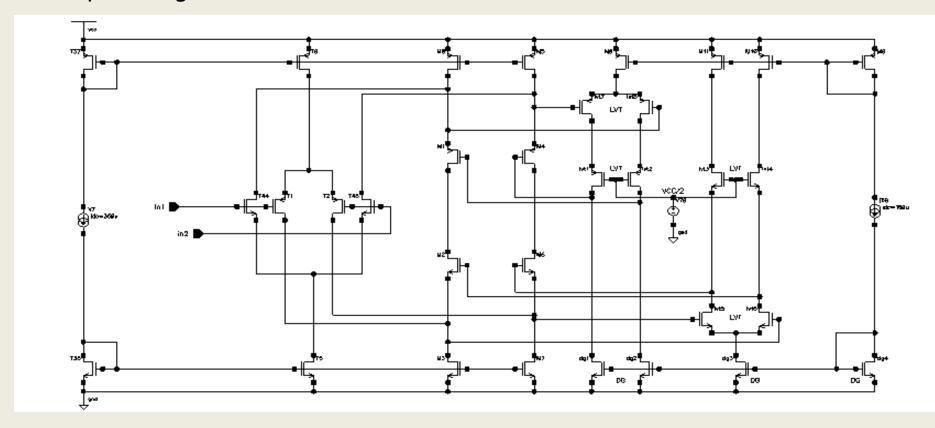

#### Portage en TSMC 130 nm

Premiers test en TSMC, premiers résultats:

Un point important pour le design est la très grande tension de seuil des transistors NMOS, ainsi que l'importance de l'effet de substrat.

La tension de seuil atteint 400 voir 500mV .... Difficile alors d'envisager d'empiler 4 transistors en région 2 avec 1.5V max. de tension d'alimentation.

A noter que les transistors NMOS LVT ont encore 350 mV de Vth alors que celui des P n'est que de 130 mV.

Après plusieurs tests pas très convaincants, je suis reparti du schéma de départ simplifié pour le début des dimensionnements.

#### TSMC: bases de dimensionnement

N et P mosiv K proche de 1 W proche de 300 N et P nmosivivt

W proche de 35

Les N en mosivt les P en mos K proche de 8 Courants de base 340 et  $170\mu A$

Tension d'alimentation 1.5V (le max ?) L fixé à 260 nm

Avec des MOS: W = 300 et K=1 !!! (Tr. Énormes, K=1 mauvais pour les P)

Avec des LVT: W=35 K=1 (Tr. « honnêtes mais K=1)

Avec les NMOS en LVT et les P en VT W=35 K=8! (pas terrible mais le moins mauvais)

#### TSMC: j'ai réalisé 5 portages: Mos, LVT, mixtes avec et sans triche les boosts sont de simples paires différentielles

| Туре                | Gain B.O. | BP. B.O. | Gain2  | BP G2-opch | V @11.5ns | Marche.Ph | Taille w/l         |

|---------------------|-----------|----------|--------|------------|-----------|-----------|--------------------|

| Mos                 | 58,8 K    | 1.1G     | 1.9996 | 378-529 M  | 499.85    | 80 Deg    | 272/260<br>308/260 |

| Tout LVT            | 50 K      | 2.4 G    | 1.9996 | 234-529 M  | 499.77    | 84 Deg    | 42-45/400          |

| LVT réduits         | 50 K      | 2.4 G    | 1.9996 | 260-700 M  | 499.77    | 86 Deg    | 20-22/400          |

| VTp LVTn            | 56 K      | 1.5 G    | 1.9997 | 230-452 M  | 499.88    | 84 Deg    | 36/330<br>240/200  |

| VTp LVTn<br>Réduits | 71 K      | 2.22 G   | 1.9998 | 320-680 M  | 499.917   | 84 Deg    | 18/260<br>130/260  |

|                     |           |          |        |            |           |           |                    |

Le meilleur produit gain bande obtenu est 27 GHz. Identique à celui obtenu en IBM 130 nm.

Jacques Lecoq Ecole in2p3 2015 FREJUS

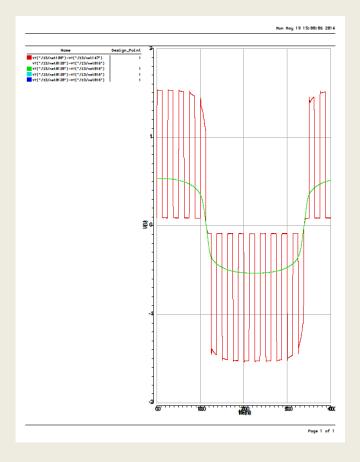

## TSMC: linéarité au gain 2 sur 1.5 V (meilleur résultats)

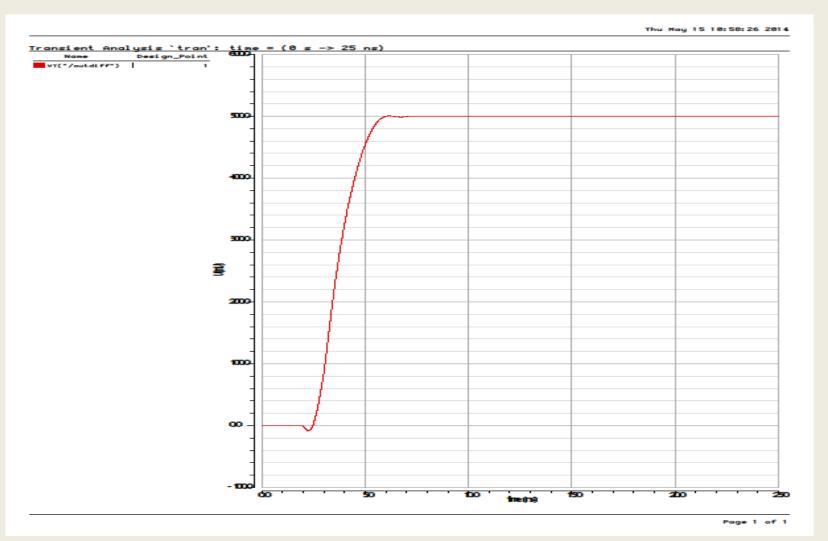

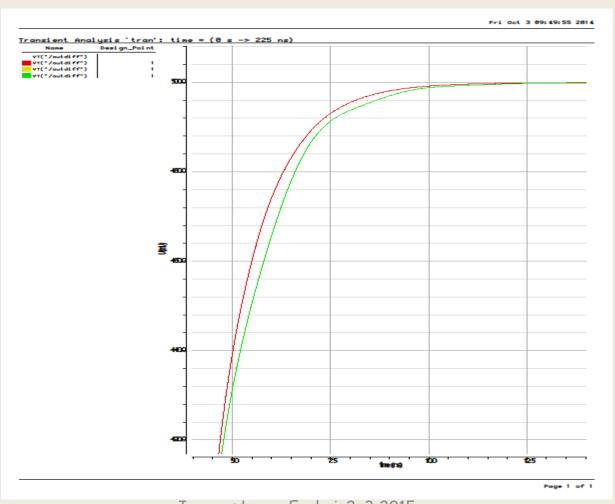

# TSMC: réponse en transitoire vert VT normaux, rouge LVTn et VTp

#### TSMC 130 nm conclusions

La technologie tsmc offre de meilleurs gm/gds qu' IBM

Donc de meilleurs gains mais

Les tensions de seuil sont nettement plus défavorables d'où

une sensibilité nettement plus marquée aux points de fonctionnement et au

mode commun. Le temps de monté est un peu moins bon.

Avec tous les transistors LVT pour les N et les P des boosts:

Tension de seuil pour les N (LVT) d'entrée Vth=366 mV Vgs=350mV Région 3!

Tension de seuil pour les P d'entrée Vth=336 mV Vgs=340mV Région 2!

Tension de seuil des N en source de courant Vth=289 mV

Avec les transistors LVT dans les boost:

Pour les N (LVT) Vth=260 mV région 3

Pour les P (LVT) Vth=163 mV région 2

Vcc/Vth= 3.5 à 3.2 pour les N, 5.5 pour les LVTN,

3.5 pour les P, presque 10 pour les LVTP.

Première constatation, les tensions de seuils me font peur!

Je mesure des tensions de seuil de 500 à 550 mV pour les N Et de 450 à 500 mV pour les P. Augmentent si W/L augmente! Avec 1.2 V d'alimentation Vcc/Vth est...proche de 2. Premiers essais: Tout se mets spontanément en région 3. De plus la tension d'Early, pour une paire diff. Varie de 1 à 2.5 V !!! Et ... diminue à L constant quand W/L augmente. Gm/Gds reste a peu près correct (22 pour un Nmos) Je tente un dimensionnement «classique »avec 1.2 V d'alimentation. Echec pour 300  $\mu$ A, même avec de très gros transistors, même en LVT.

En procédant cette fois ci par tâtonnement, on arrive à trouver un point de fonctionnement pour l'ampli sans ses boosts.

Le gain est assez faible, mais par tâtonnement, on fini par obtenir 350.

Même problème qu'en AMS 0.18  $\mu$  pour les boosts: Il faut ajouter un suiveur, une seule paire à étudier, mais le gain des tombe à 30, et il faut une capacité pour aider les suiveurs ...En plus le dimensionnement des suiveurs fixe le mode commun ...

- $\Rightarrow$  Il faut cascoder les boosts, et tout va mieux.

- $\Rightarrow$  Le gain des boosts atteint 100 et leur produit gain bande 3 GHz.

- ⇒ Le dessin des boosts est nettement moins évident qu'en 130nm

Bref, pour le même cahier des charges Avec un dimensionnement « à taton » et des boosts cascodés On arrive péniblement à un gain de 35K et un produit gain bande de 4.9 GHz. Les tailles optimales des transistors des cascodes « N » sont  $72\mu/280n$  Et pour les « P »  $168\mu/280n$

En utilisant des LVT pour les cascodes « N » on peut réduire leurs tailles. On améliore un peu le produit gain bande à 5.8 GHz pour le même gain

En utilisant des LVT pour les cascodes « N et P » On améliore encore le produit gain bande à 6.7 GHz pour le même gain (35k) Cela devient utilisable bien que 5 fois moins bon qu'en 0.13  $\mu$ m

Reste que le produit gain bande est encore un peu faible Du coup la signal max. en sortie du montage ADC n'est que de 499.58 mV à 11.5 ns

Avec 1.4V d'alimentation, le dimensionnement classique est « possible ». 1.4V « semble supportable par cette techno » On prend soins qu'aucun Vds ne puisse dépasser 1.2 V.

Le gain sans boosts est de 600-800

Avec des boosts cascodés on obtient un gain de 74k

Paire N, région 3, Vth=530 mV, 100  $\mu$ A, Vearly=1 V, W/L=36 $\mu$ /160n

Cascode N, région 3, W/L=48µ/180n

Charges P, région 2, Vearly=6 V, W/L= $10\mu/425n$

#### Portage en TSMC 65 nm: Résultats

Alimentation 1.4V (aucun transistor ne dépassant 1.2 V de Vds) Boosts cascodés, avec suiveurs et capas.

Gain 74000, produit gain bande 6.4 GHz Sur le banc de test « ADC » (charge 2.4 pF): Marge de phase 84° Tension dans le cas le plus défavorable à 11.5 ns 0.499936 V pour 0.5 V. Transistors ampli:

Tous en région 3 (sauf les sources de courant)

Entrée: N Vth=549 mV, Vgs=418 mV, W/L=210μ/180n

Entrée: P Vth=493 mV , Vgs=449 mV, W/L=240 $\mu$ /180n

cascodeN: Vth=528mV, W/L=44 $\mu$ /280n, cascode P: Vth=470mV, W/L=112 $\mu$ /280n

Source de courant: N W/L=160 $\mu$ x520n, P: W/L=190 $\mu$ x480n

Boosts:

Paire N, région 3, Vth=530 mV, Vgs=446 mV,100  $\mu$ A, Vearly=1 V, W/L=36 $\mu$ /160n Cascode N, région 3, W/L=48 $\mu$ /180n Charges P, région 2, Vearly=6 V, W/L=10 $\mu$ /425n

#### Portage en TSMC 65 nm: Conclusion

- Avec 1.2 V d'alimentation, c'est vraiment trop juste pour ce courant.

- Avec 1.4 V d'alimentation, on obtient des résultats.

- Les 2 études ont été menées jusqu'au bout, contre réaction de mode commun comprise.

#### Région 3

- ⇒ points de fonctionnement beaucoup plus sensibles

- $\Rightarrow$  CMFB pour les boosts?

- =>Il n'y a quasiment plus de réjection au mode commun!

- => Le design des boosts est nettement plus délicat (suiveurs, capas, cascodes....)

- =>Le produit gain bande diminue à nouveau....

- =>Curieusement, la linéarité est exceptionnelle?

- Il ne s'agit « que » d'une simulation, aucune fonderie n'ayant été réalisée en 65 nm

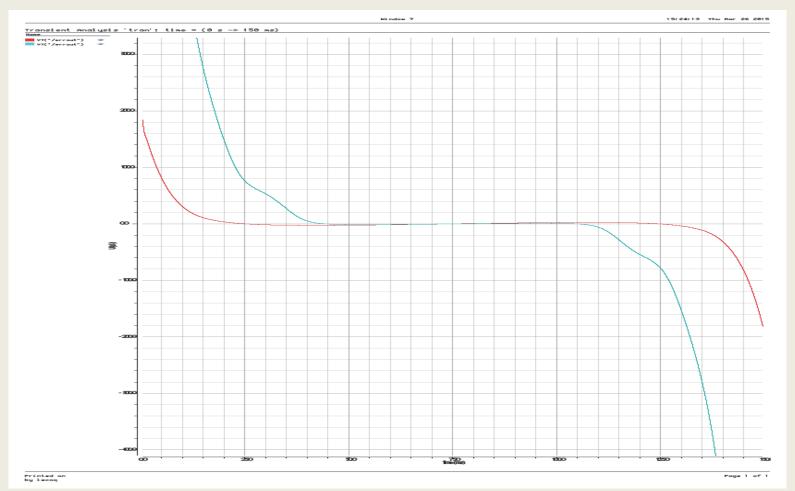

### Erreur à la linéarité sur 2 V

Gains normalisés à 1.9999 pour 1.4 V et à 1.9998 pour 1.2 v d'alimentation En 1.4V l'erreur est de 200nV/1V, de  $5\mu$ V/1.5V et de  $180\mu$ V/2V En 1.2V l'erreur est de  $300\mu$ V/1V, de  $160\mu$ V/1.5V et de 3mV/2V.

## Comparateurs analogiques à grand produit gain bande

Origine via AMS (comparateur de l'ADC 10 bits du kit AMS) Et via Samuel qui l'a trouvé dans la littérature et utilisé dans Féeric. Etude faite au départ en AMS 350nm.

L'architecture m'a semblée suffisamment intéressante pour tenter De l'optimaliser, de la passer en différentiel et de l'essayer dans les différentes technologies.

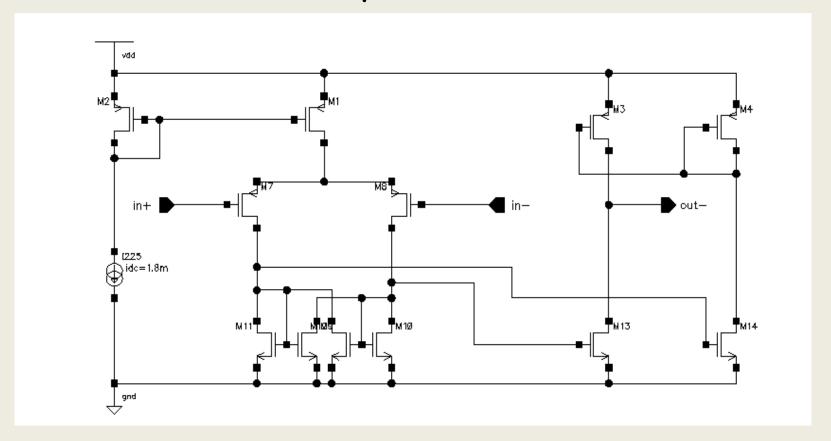

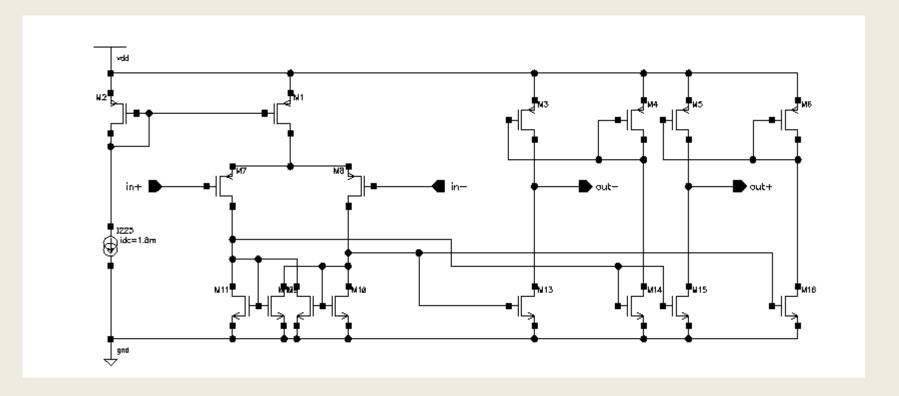

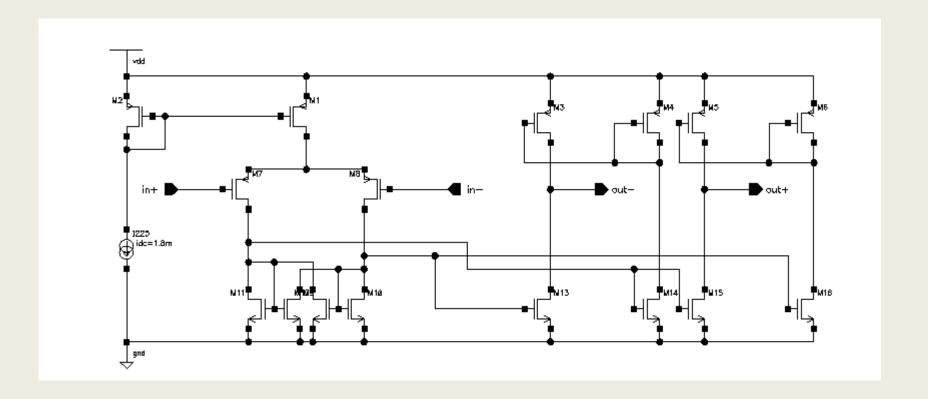

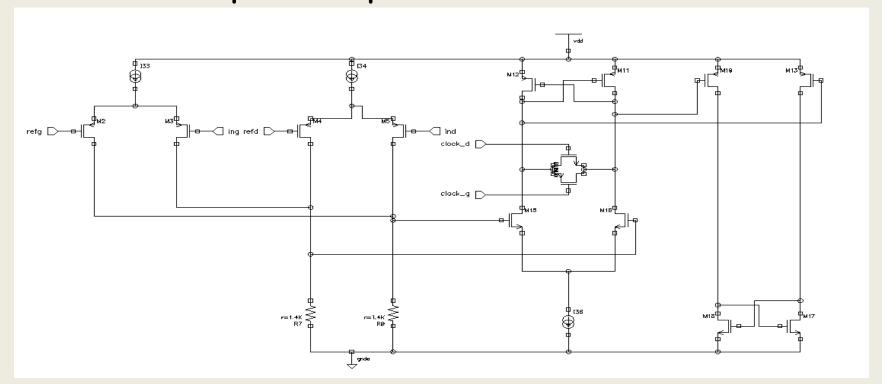

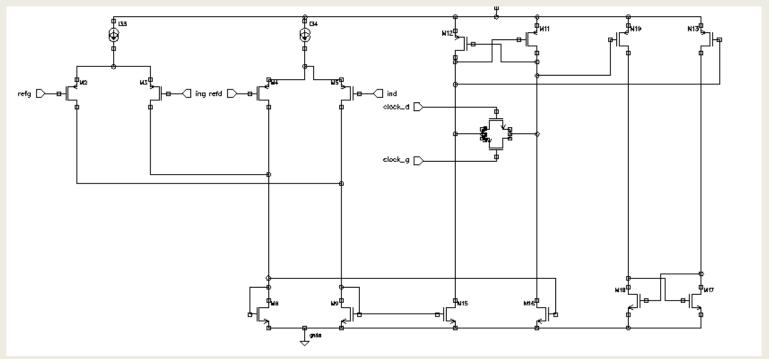

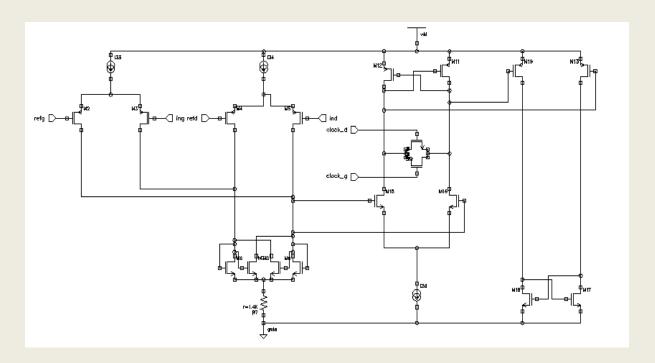

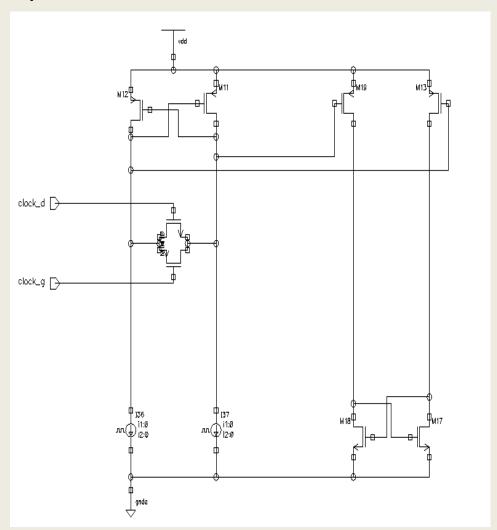

## schéma de départ en AMS 350 nm

Simple et symétrique Auto polarisé Transformable facilement en différentiel sans CMFB Capable d'attaquer directement les cellules digitales.

### schéma de départ en AMS 350 nm

Très facile à dimensionner (du moins en AMS 350 nm)

La charge est astucieusement faite de 4 transistors égaux,

le gain est au premier ordre indépendant de leur taille.

Avec 1.8 mA en entrée, en optimalisant un peu, on obtient facilement

Un gain de 4 K et un produit gain bande De 65 GHz

Jacques Lecoq Ecole in2p3 2015 FREJUS

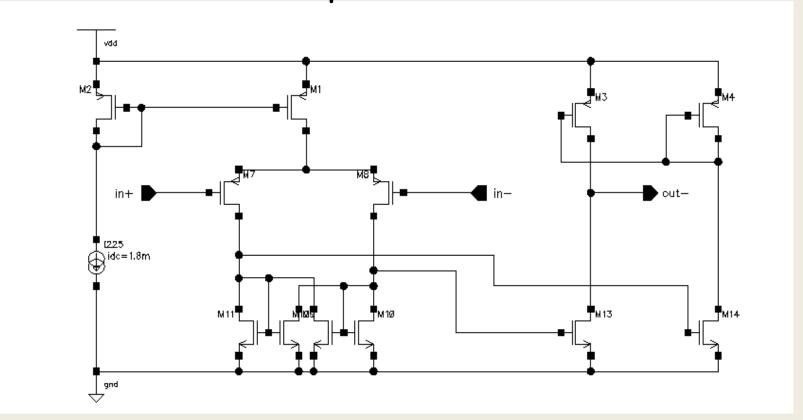

### Si on passe en différentiel

Avec le même courant et les mêmes transistors , on obtient facilement Un gain de 8 K et un produit gain bande De 100 GHz

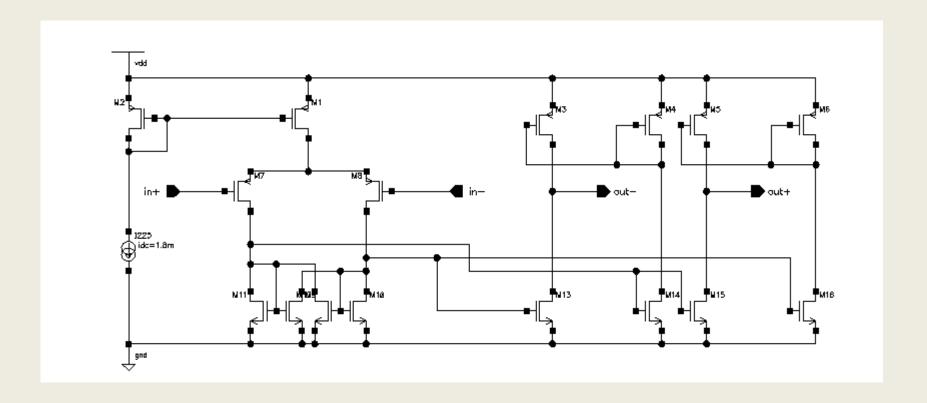

### Si on utilise des bipolaires

Triple avantage: on garde l'avantage de l'entrée MOS.

On améliore le gain en entrée (meilleur gds)

On améliore le gain en sortie (meilleur gm)

On obtient alors un gain de 32K et un produit gain bande de 140 GHz

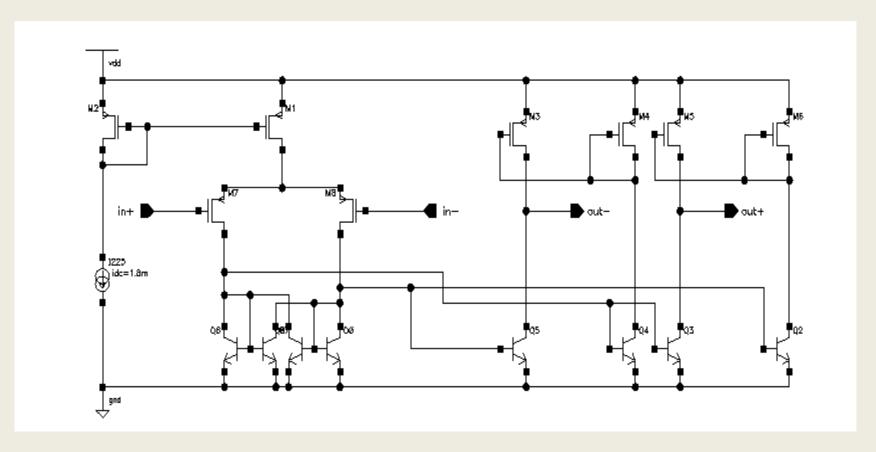

### Portage en AMS 180 nm

Dans les mêmes conditions avec 1.8 mA en entrée, On n'obtient que 1.5 K de gain, et le produit gain bande Chute à 22 GHz. (facteur 3 par rapport au 350 nm) En y regardant de plus près c'est le Gds qui pénalise le plus En augmentant d'un facteur 3.

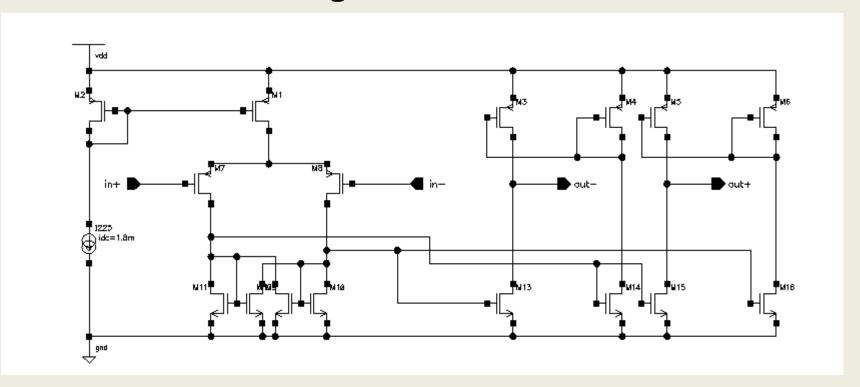

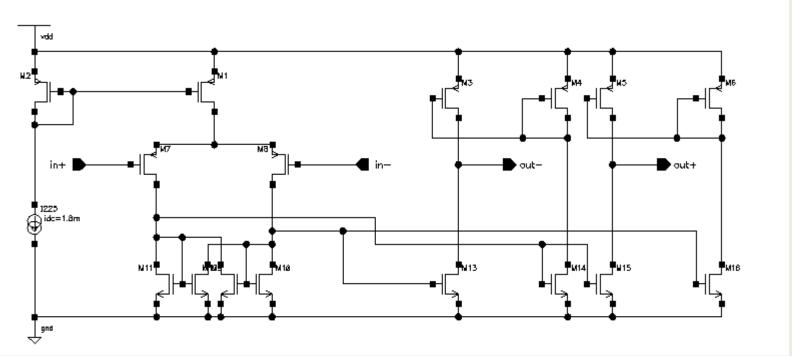

### AMS 180 nm en différentiel

Avec le même courant et les mêmes transistors, on obtient sans surprise un gain de 3K et un produit gain bande De 26 GHz. (perte d'un facteur 3 par rapport au 350 nm)

### Portage en AMS 180 nm

En faisant varier tous les paramètres, je cherche le meilleur produit gain bande.

En faisant varier le courant, on trouve (en différentiel)

Pour 1.8 mA, G=3k, et un produit gain bande de 22 GHz

Pour 1.2 mA, G=3.2k, et un produit gain bande de 30 GHz

Pour 1 mA, G=3.6k, et un produit gain bande de 28.8 GHz

Pour 1.2 mA, G=4k, et un produit gain bande de 26 GHz

Après optimalisation, on ne perd qu'un facteur 2 par rapport au 350 nm, et la consommation est 3 fois plus faible.

On est cependant très loin de la version AMS avec bipolaires.

### Portage en IBM 130 nm

Mêmes conditions avec 1 mA en entrée, J'ai beaucoup de mal ...

La paire différentielle d'entrée a peu de gain : 25 au plus ....

L'étage de sortie très peu de produit gain bande.

En y regardant de plus près, la liaison des deux étages n'est pas efficace du Fait du faible seuil des nmos. Le facteur gm/gds est très mauvais en sortie. Du coup on gagne à mettre des lvt en charge de l'étage d'entrée.

Mais j'arrive péniblement à 350 de gain et 20 GHz de produit gain bande.

### Portage en IBM 130 nm

J'essaye un peu tout, sans grand résultat.

Je cherche le moins mauvais gm/gds en entrée... le gain passe à 32 ... Je cherche ensuite le moins mauvais gm/gds en sortie.... Le rapport gm/gds des nmos est vraiment trop mauvais... En modifiant le schéma et en plaçant une vraie paire différentielle en sortie, on améliore, mais on reste relativement peu performant. (1k, 25GHz)

J'essaye alors de remplacer les nfet ou lytnfet par des dgnfet (2.5 V)

Le rapport gm/gds grimpe à 200 !!!! , avec 800  $\mu$ A.

J'obtiens sans peine un gain de 1.9K avec un produit gain bande de 53 GHz Et, en différentiel, un gain de 3,88K et un produit gain bande de 84 GHz Ce qui est un excellent résultat, quasiment aussi bon qu'en AMS 350 Et en consommant 3 fois moins.

J'essaye de remplacer aussi les pfet par des dg, mais là c'est un peu moins bon.

### Portage en TSMC 130 nm

Idem, avec 0.8 mA en entrée, marche quasiment du premier coup!!

On consomme encore un peu moins (1.5 V d'alim) Le gain obtenu est de 2.1 K et le produit gain bande de 43 GHz En différentiel:

4.2 K et un produit gain bande de 66 GHz.

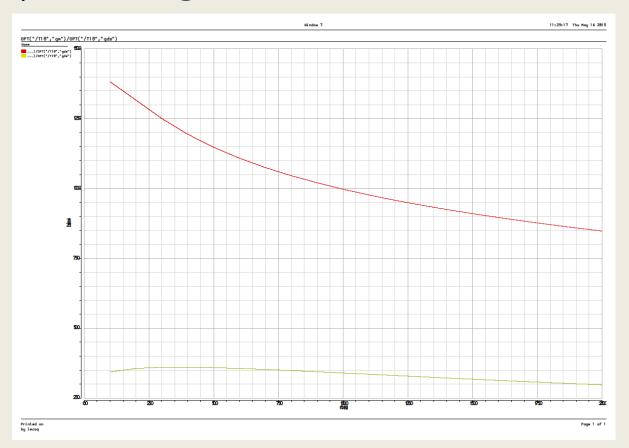

### Et en TSMC 65 nm

C'est la bonne surprise, marche quasiment du premier coup!! On consomme encore moins (0.5 mA et 1.4V d'alim) MAIS:

Le gain obtenu n'est que de 1 K mais le produit gain bande est de 80GHz En différentiel:

2 K et un produit gain bande de 143 GHz. Si on augmente le courant, c'est moins bon

### TSMC 65 nm

On voudrait augmenter le gain.

La cause de la perte de gain est le mauvais rapport gm/gds

<u>En particulier ici le mauvais gds des pmos.</u>

Essais avec les transistors de 2.5 V - ECHEC

Pour les N cela n'apporte rien (c'est même moins bon)

Pour les P c'est bien pire. La tension de seuil atteint 650 mV

⇒ Impossible de trouver un point de fonctionnement.

Si on regarde l'allure de la courbe gm/gds = f(ids), la seule solution, c'est de diminuer le courant. (on peut se le permettre ici, il n'y a pas de charge, ni PB de stabilité) En faisant varier le courant, on obtient:

Pour 500  $\mu$ A un gain de 2K et un produit gain bande de 143 GHz Pour 180  $\mu$ A un gain de 2,8K et un produit gain bande de 93 GHz Pour 90  $\mu$ A un gain de 3,5K et un produit gain bande de 61.5 GHz Certes ce n'est pas de l'AMS 350nm, mais on consomme 20 fois moins

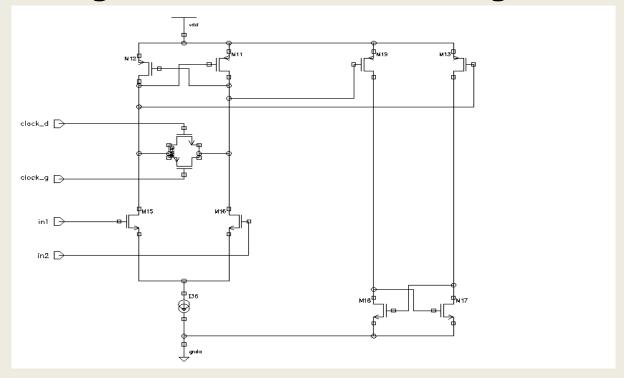

## Les comparateurs synchrones (Latchés) et leurs intégrations dans un montage différentiel

Montage de base bien connu: Grande sensibilité (jusqu'à 1µV) Rapide A courant constant Génère du kick back noise switches à Vcc/2

## Etude (simple) des switches Résistance en fonction du signal.

En MOS, l'interrupteur se réalise très simplement en utilisant un seul transistor MOS. La commande est la tension grille: Dès que Vgs dépasse la tension de seuil Vt, le transistor se met à conduire, et si Vgs» Vt l'interrupteur est considéré comme fermé. Cependant, la résistance « on » de l'interrupteur n'est Pas fixe, mais dépend de Vgs, et de Vds.

$$R = \frac{1}{\mu.Cox.W.((Vgs-Vt)-Vds)}$$

Si l'interrupteur est assez bien fermé, Vds est très Faible et on peut le négliger, mais Vgs, en général Dépend du signal. On se trouve donc en présence D'un interrupteur dont la qualité est fonction Du signal appliqué ....

## Etude (simple) des switches Résistance en fonction du signal.

Pour un pmos seul

## Etude (simple) des switches Résistance en fonction du signal.

Montage de base bien connu, nmos et pmos en parallèle, avec un Pmos dimensionné pour obtenir un Ron identique au N.

On fait varier le signal de +- 0.5V autour de Vcc/2. On mesure Ron en fonction du signal.

Jacques Lecoq Ecole in2p3 2015

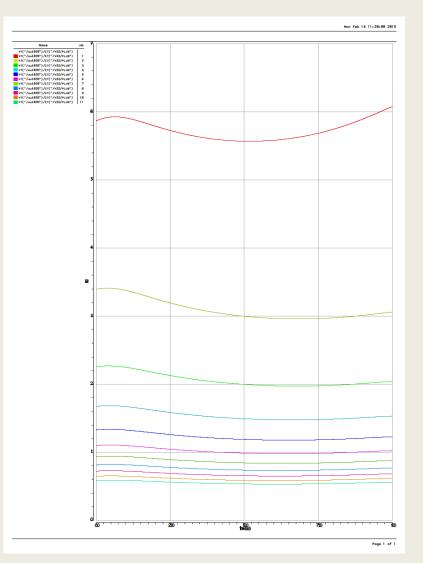

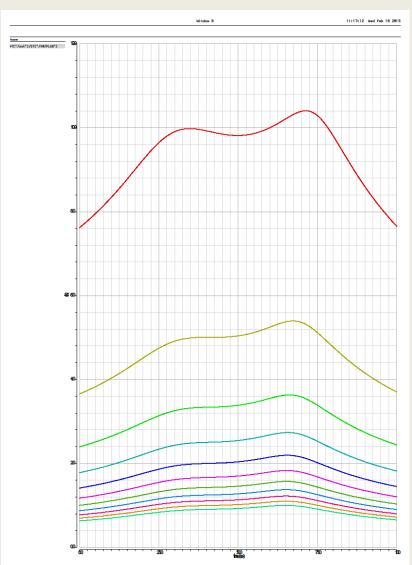

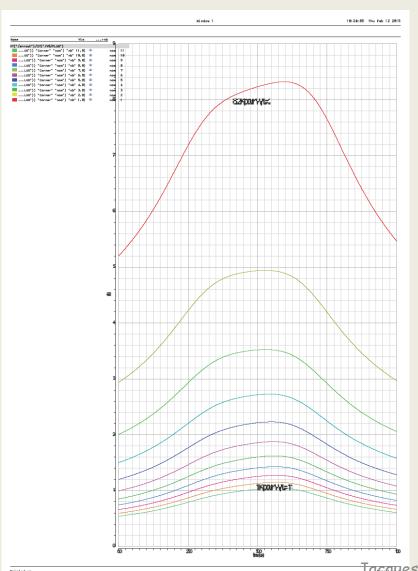

# Résistances des switches complémentaires en technologie AMS 350 nm

Transistors utilisés: nmos4 et pmos4

L=350nm, W varie de 400nm à 4400nm pour les N Et de 1600 à 17600 pout les P Rapport P/N pour équilibrer RON: 4

Alimentation, 3 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 4.5K à 6k

Pour W maxi (vert) R quasi constant à 300 Ohms

A noter la très faible variation de RON sur 1V

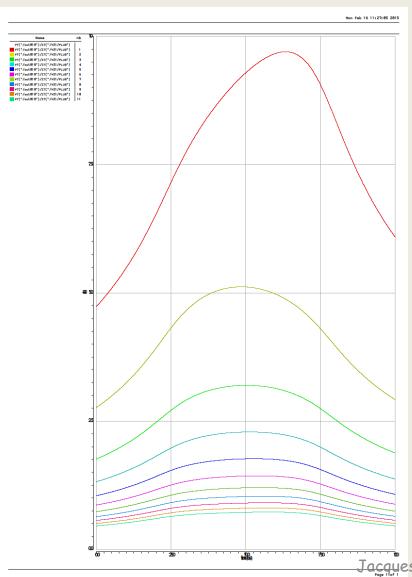

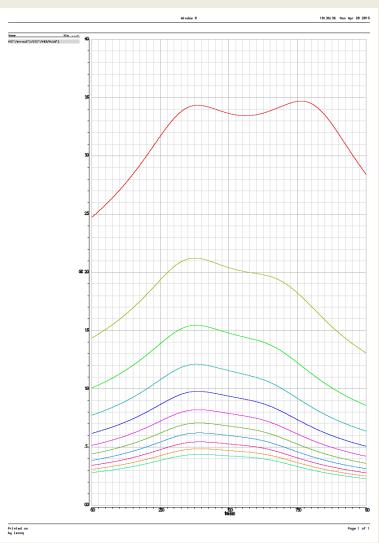

# Résistances des switches complémentaires en technologie AMS 180 nm

Transistors utilisés: nfet et pfet

L=180nm, W varie de 180nm à 1980nm pour les N Et de 720 à 7920 pout les P Rapport P/N pour équilibrer RON: 4

Alimentation, 1.8 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 40K à 80k

Pour W maxi (vert) R varie de 4k à 6K

NB. On peut faire mieux si on augmente W/L du NMOS, mais il y a prédominance du N.

Jacques Lecoq Ecole in2p3 2015

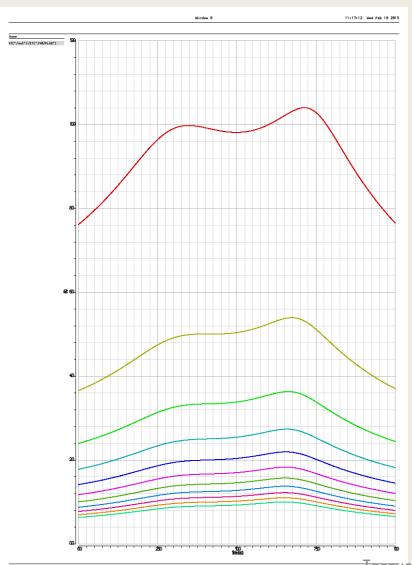

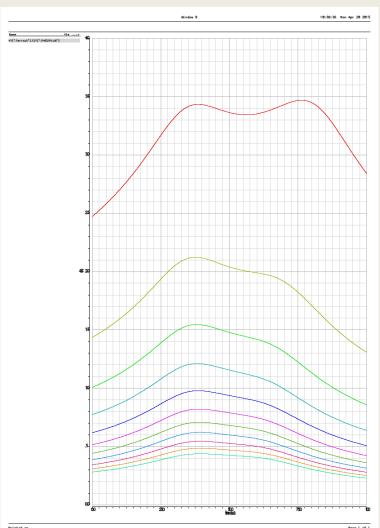

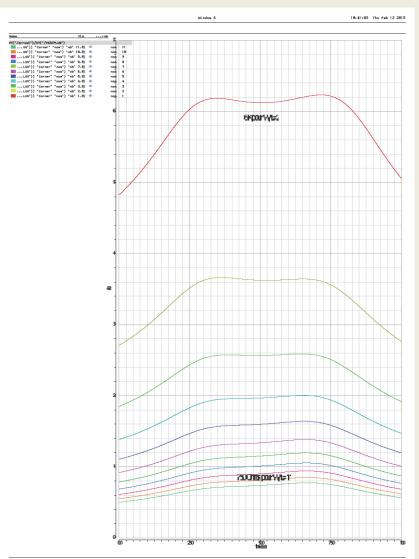

# Résistances des switches complémentaires en technologie IBM 130 nm

#### Transistors utilisés: nfet et pfet

L=120nm, W varie de 160nm à 1760nm pour les N Et de 560 à 5160 pout les P Rapport P/N pour équilibrer RON: 4.8

Alimentation, 1.6 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 7.5K à 10k

Pour W maxi (vert) R varie de 700 Ohms à 1K

NB. On peut faire mieux si on augmente W/L du NMOS, mais il y a prédominance du N.

Jacques Lecoq Ecole in2p3 2015

# Résistances des switches complémentaires en technologie IBM 130 nm

Transistors utilisés: nfet\_lvt et pfet\_lvt

L=120nm, W varie de 160nm à 1760nm pour les N Et de 560 à 5160 pout les P Rapport P/N pour équilibrer RON: 4.8

Alimentation, 1.6 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 6.9K à 8.5k

Pour W maxi (vert) R varie de 570 à 710 Ohms

NB. On peut faire mieux si on augmente W/L du NMOS, mais il y a prédominance du N.

# Résistances des switches complémentaires en technologie TSMC 130 nm

Transistors utilisés: nmos1v et pmos1v

L=120nm, W varie de 150nm à 1650nm pour les N Et de 700 à 7700 pout les P Rapport P/N pour équilibrer RON: 4.66

Alimentation, 1.5 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 2.5K à 3.35k

Pour W maxi (vert) R varie de 300 à 430 Ohms

NB. On peut faire mieux si on augmente W/L du NMOS, mais il y a prédominance du N.

# Résistances des switches complémentaires en technologie TSMC 130 nm LVT

#### Transistors utilisés: nmos1vlvt et pmos1vlvt

L=120nm, W varie de 150nm à 1650nm pour les N Et de 600 à 6600 pout les P Rapport P/N pour équilibrer RON: 5

Alimentation, 1.5 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 2.35K à 2.7k

Pour W maxi (vert) R varie de 220 à 250 Ohms

NB. On peut faire mieux si on augmente W/L du NMOS, mais il y a prédominance du N.

# Résistances des switches complémentaires en technologie TSMC 65 nm

#### Transistors utilisés: nch et pch

L=120nm, W varie de 120nm à 1440nm pour les N Et de 300 à 3300 pout les P Rapport P/N pour équilibrer ron: 2.5

Alimentation, 1.2 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 65K à 200k

Pour W maxi (vert) R varie de 7k à 45K

# Résistances des switches complémentaires en technologie TSMC 65 nm

Transistors utilisés: nch\_lvt et pch\_lvt

L=120nm, W varie de 120nm à 1440nm pour les N Et de 300 à 3300 pout les P

Même rapport P/N (2.5)

Alimentation, 1.2 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 5K à 9.2k

Pour W maxi (vert) R varie de 0.5k à 1.2K

# Résistances des switches complémentaires en technologie TSMC 65 nm

Transistors utilisés: nch\_lvt et pch\_lvt

L=120nm, W varie de 120nm à 1440nm pour les N Et de 300 à 3300 pout les P

Même rapport P/N (2.5)

Alimentation 1.4 V

Signal +- 500 mV.

Pour W mini (rouge) R varie de 4K à 6k

Pour W maxi (vert) R varie de 500 à 750 Ohms

Résultats assez favorable compte tenu des tensions d'alimentation et de seuil.

by lecoq

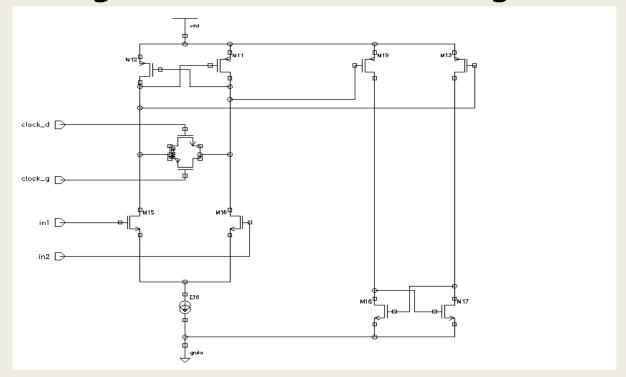

## Les comparateurs synchrones (Latchés) et leurs intégrations dans un montage différentiel

Montage de base:

Grande sensibilité (jusqu'au  $\mu V$  en simulation,  $100\mu V$  en test)

Rapide (testés au delà du GHz)

A courant constant

Génère du kick back noise (switches à Vcc/2)

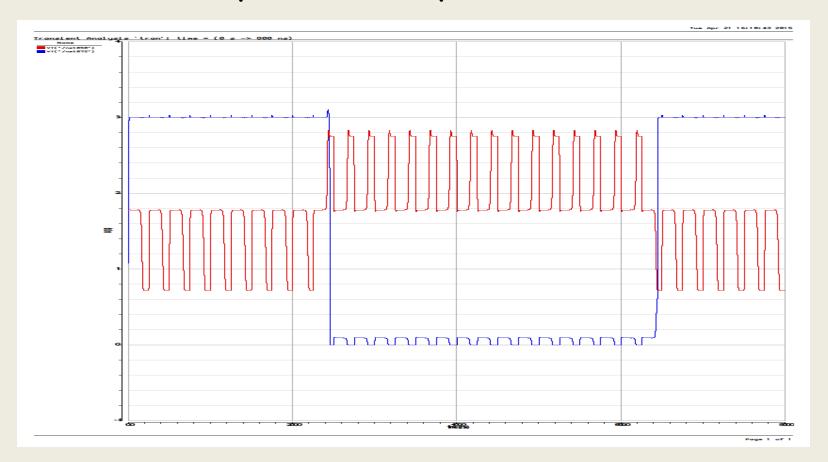

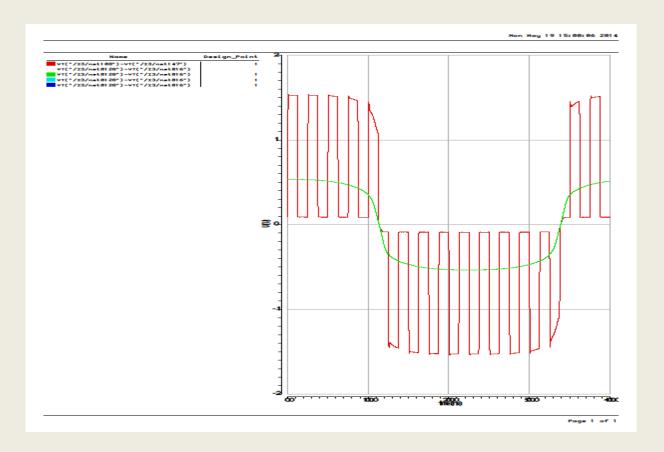

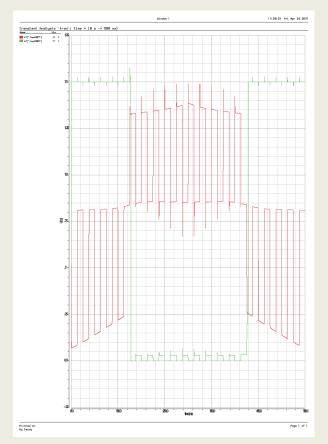

## Les comparateurs synchrones (Latchés)

Pour rappel, les signaux de sortie du premier étage (rouge), et ceux du deuxième (bleu), quasiment digitaux.

Ici en AMS 350nm.

Remarque: la tension aux bornes des switches fermés est à Vcc/2

## Un étage d'entrée supplémentaire

Pour:

Réduire le kick back noise

Et/ou augmenter le gain, la sensibilité, réduire l'offset.

Passer de 2 à 4, 6 entrées ou plus pour:

- Passer en différentiel

- Faire du moyennage dans les ADC flash à échelle différentielle

## L'étage d'entrée supplémentaire le plus simple : des résistances

On a un peu de gain.

Le point de fonctionnement de sortie (proche de Vcc/2) est facile à trouver, l'impédance de sortie est élevée donc faible rejet du kick back noise. Si le signal de sortie est trop grand, risque de déclenchement asynchrone

# Etage d'entrée supplémentaire passer en courant

Faible impédance de sortie, bonne réjection au kick back noise On n'est plus à courant constant, le courant dépend du signal Le signal vu par les switches n'est plus limité en courant Il y a un fort risque de déclenchement asynchrone. On peut durcir les switches ou les mettre carrément à la masse Mais cela augmente le bruit.

## Etage d'entrée supplémentaire utiliser des diodes en charge active

impédance de sortie relativement faible (il faut des W/L petit Pour avoir un point de fonctionnement correct à Vcc/2) Peu de gain

Mais effet de compresseur très intéressant élimine les déclenchements Asynchrones (gain pour petits signaux moins de gain pour les grands)

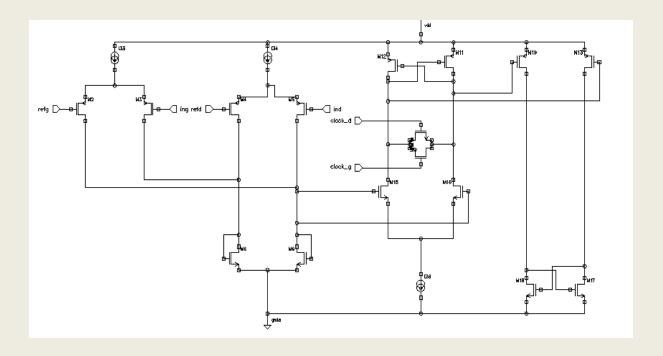

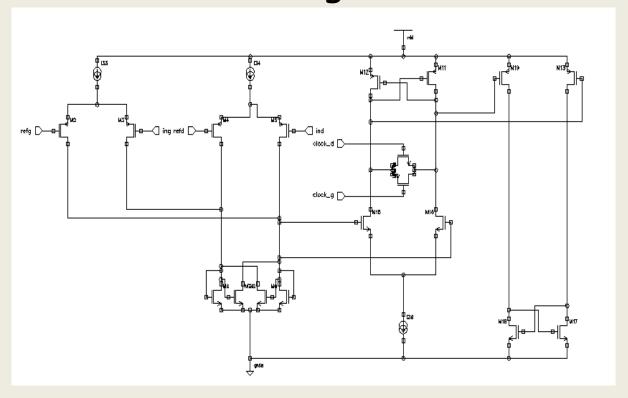

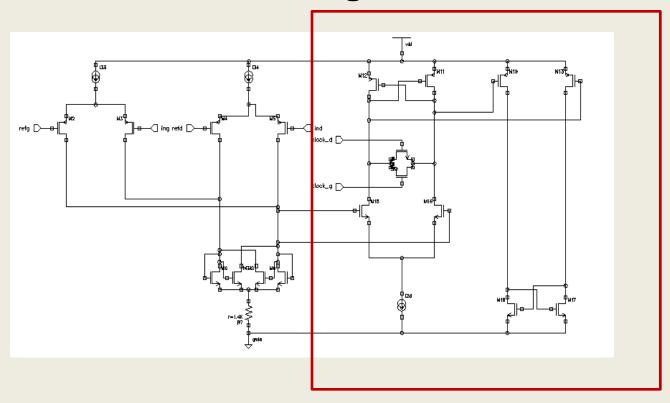

## Etage d'entrée supplémentaire utiliser le montage 4 transistors

L'effet de compresseur est très intéressant élimine les déclenchements Asynchrones (grand gain pour petits signaux pas de gain pour les grands) Très nette amélioration du gain et du produit gain bande

Il faut toujours des W/L petit à cause du point de fonctionnement.

## Amélioration: ajouter une résistance

L'effet de compresseur est très intéressant élimine les déclenchement Asynchrones (grand gain pour petits signaux pas de gain pour les grands) Très nette amélioration du gain et du produit gain bande

On peut mettre des grands W/L:

Triple avantage: le compresseur est bien meilleur, l'impédance est plus faible Et le point de fonctionnement s'ajuste avec la résistance.

### Résultats

Avec 120  $\mu$ A dans l'étage d'entrée 90  $\mu$ A dans la paire différentielle intermédiaire 50  $\mu$ A dans celle de sortie Le gain est de 8 pour les petit signaux, de 1 pour les grands

## Résultats

Aucun risque de déclenchement asynchrone. Les deux points de fonctionnement sont à Vcc/2

## Portages

Portages restreints au dernier étage. (le premier a déjà été traité) On regarde la sensibilité, la consommation et la vitesse Sur quelques exemples pour chaque techno.

## Résultats en AMS 350nm Plusieurs ex. fondus et testés

Ex pour des comparateurs à 40 MHz:

Alimentation: 3V

Entrée: 100μA, sortie 30μA

Sensibilité: 10µV

Ex à 100 MHz, Bipolaire ou mos en entrée Entrée 300μA, sortie 60 μA Sensibilité: 2μV

Ci contre une variante pour un comparateur de courant Sensibilité 50pA

## En AMS 350nm, le confort ...

sortie

Ex pour des comparateurs à 40 MHz:

Alimentation: 3V

Entrée: mos

Sensibilité: 10µV

Ex à 100 MHz,

Bipolaire ou mos en entrée

Entrée 300μA, sortie 60 μA

Sensibilité: 2µV

La variante pour le comparateur de courant

*A*lim 1.8V

Sensibilité 50pA

Mode commun du signal: 1.5V

Taille de switches:  $2\mu/350n$

$80\mu/400n$ , charge 4/400n

P:  $2.5\mu/350n$ , N:  $1\mu/350n$

Même mode commun

Taille des switches  $4\mu/350n$

npn121 ou mos  $50\mu/800$ n

sortie P:5 $\mu$ /350n, N: 1 $\mu$ /1 $\mu$

Courant de repos 50µA

sources de courant:  $30\mu/1.6\mu$

Taille des switches  $5\mu/350n$

sortie P:5 $\mu$ /350n, N: 1 $\mu$ /1 $\mu$

On peut travailler à courant plus faible, excellente sensibilité. Facilité et souplesse de dimensionnement.

Seul bémols: Vitesse (relatif) et (relative) consommation.

Jacques Lecoq Ecole in2p3 2015 FREJUS

# Résultats en AMS 180nm simulations seules

Alimentation en 1.8V, mode commun des signaux d'entrée 900mV.

Pas de difficultés particulière, marche « du premier coup » On peut utiliser des transistors plus petits, on va plus vite... Un exemple:

Ex pour des comparateurs à 100 MHz:

Courant d'entrée dans la paire différentielle: 30µA

Transistors d'entrée N:  $6\mu/300n$ , charges P:  $4\mu/500n$

En sortie, P:  $1\mu/200n$ , charge N: 500n/500n

Switches N et P:  $1\mu/180n$

Sensibilité obtenue:  $10\mu V$

=> On n'est pas gênés par les tensions de seuil (2 transistors)

# Résultats en IBM 130nm (Plusieurs ex. fondus et testés)

Alimentation en 1.6V, mode commun des signaux d'entrée 800mV.

Pas de difficultés particulière, marche « du premier coup » On peut utiliser des transistors encore plus petits.

Exemple avec de tout petits transistors:

Fréquence: 40 MHz

Courant d'entrée dans la paire différentielle:  $90\mu A$ Transistors d'entrée N:  $8\mu/120n$ , charges P:  $1\mu/120n$

En sortie, P: 800n/120n, charge N: 160n/120n

Switches N et P: 400n/120n

Sensibilité: 100 µV

# En IBM 130nm à 1GHz (fondu et testé)

Courant d'entrée dans la paire différentielle: 300µA

Transistors d'entrée N:  $30\mu/120n$ , charges P:  $6\mu/120n$

En sortie, P:  $5\mu/120n$ , charge N: 500n/200n

Switches N et P:  $2\mu/120n$

Sensibilité obtenue:  $20\mu V....$  à 1GHz Bruit en transitoire simulé à  $168 \mu V.$

## En TSMC 130nm

## En IBM 130 nm

Portage calqué sur IBM 130nm, tailles de transistors similaires, tension et courant identique:

Le problème est le Ron des switches, lié à la tension de seuil

## En TSMC 130nm

## En IBM 130 nm

#### Solution:

Utiliser pour les switches des lvt's et augmenter le W/L d'un facteur 4 Pour réduire le Ron => résultat correct.

Dans ces conditions, la sensibilité passe de plus de  $100\mu V$  à moins de  $10~\mu V$

## ?????? Et en TSMC 65nm ??????

Alimentation en 1.2V, mode commun des signaux d'entrée 600mV.

On a le même problème, en plus accentué qu'en TSMC 130nm.

Le Ron de switches est élevé du fait de la tension de seuil élevée et de la faible tension d'alimentation. Dans les mêmes conditions et avec les mêmes tailles de transistors:

En entrée au repos Vth=545mV, Vgs=550mV et Vearly=1,9V...

Avec le signal, les transistors changent de région

Les switches se ferment très mal => risque de déclenchement asynchrone

Des Lvt's pour les switches améliorent. Le problème des Vth restent. Cela semble marcher quand même ?

## ?????? Et en TSMC 65nm ??????

Si on utilise des Lvt's aussi pour la paire différentielle d'entrée c'est mieux

Si on passe en 1.4V d'alimentation c'est encore mieux. Mais il faut des transistors plus gros qu'en 130 nm! La sensibilité est meilleure?

Entrée  $90\mu A$ , sortie  $13\mu A$

W/L: en entrée N=6 $\mu$ /240n, P=1.8 $\mu$ /80n en sortie P=400/100n, N=120/80n switches N et P 1 $\mu$ /80n

Sensibilité (simulée)  $5\mu V$

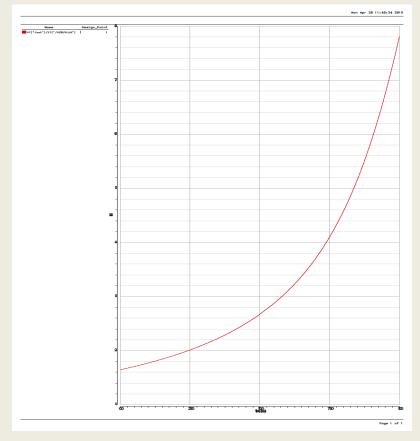

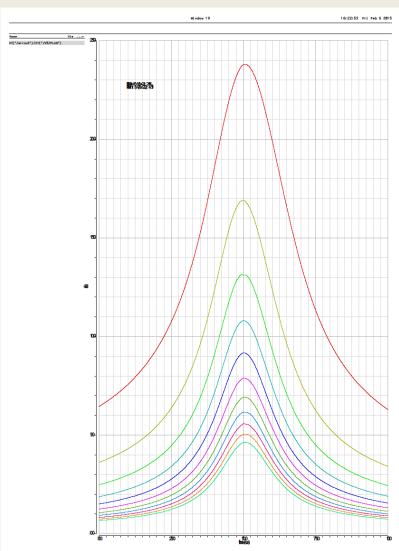

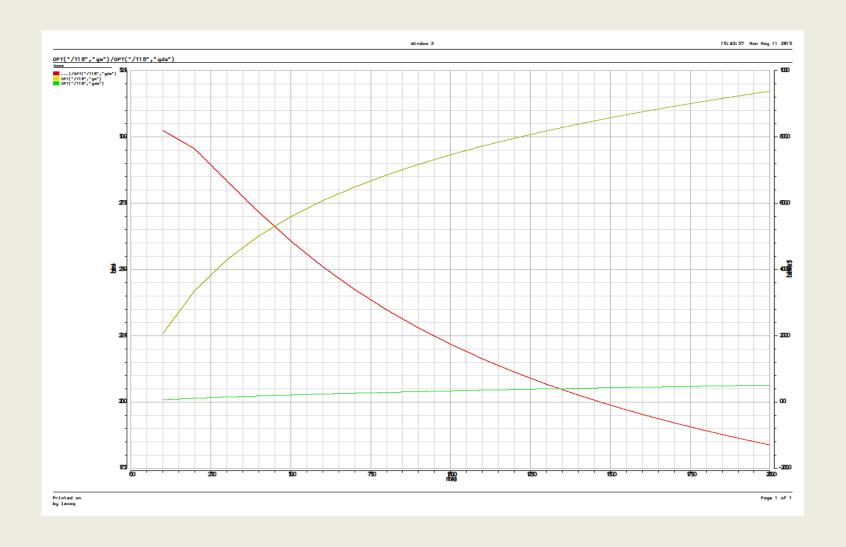

## Un ou deux paramètres pour terminer

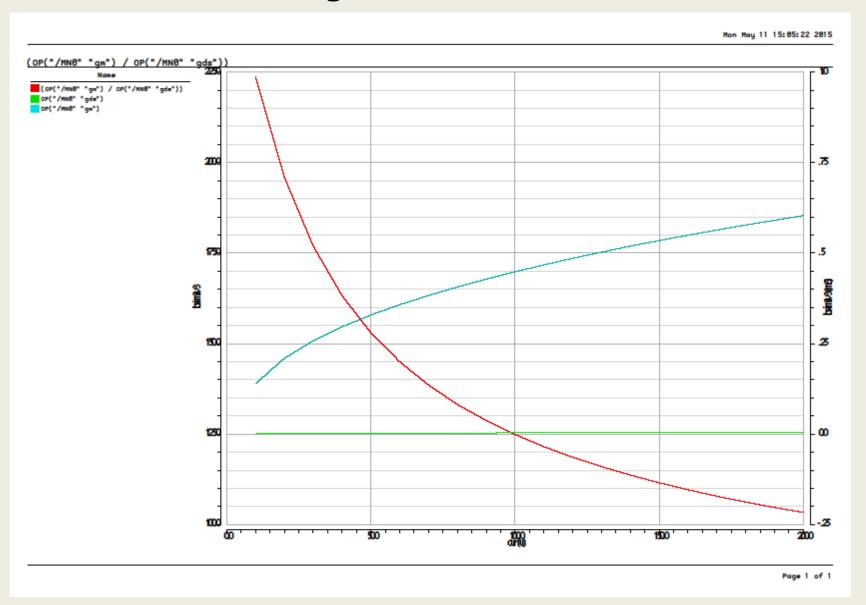

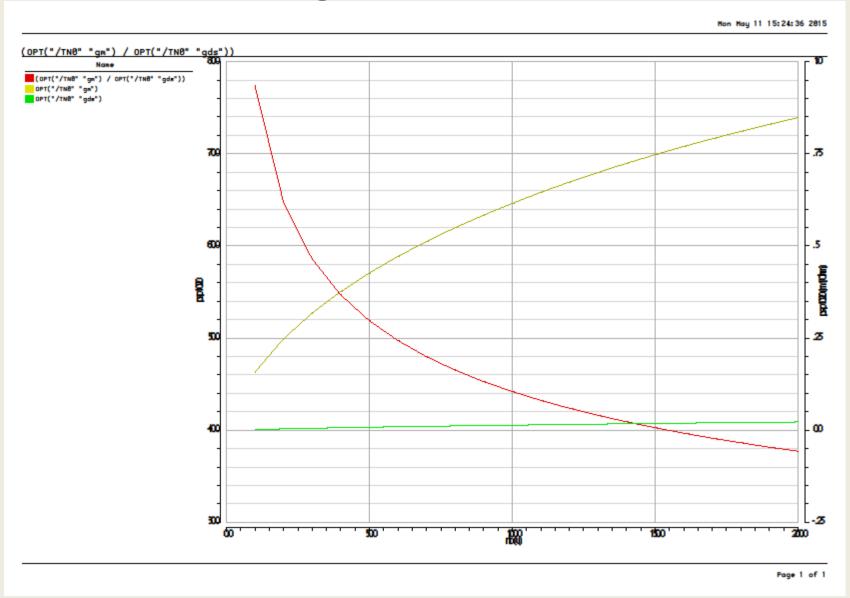

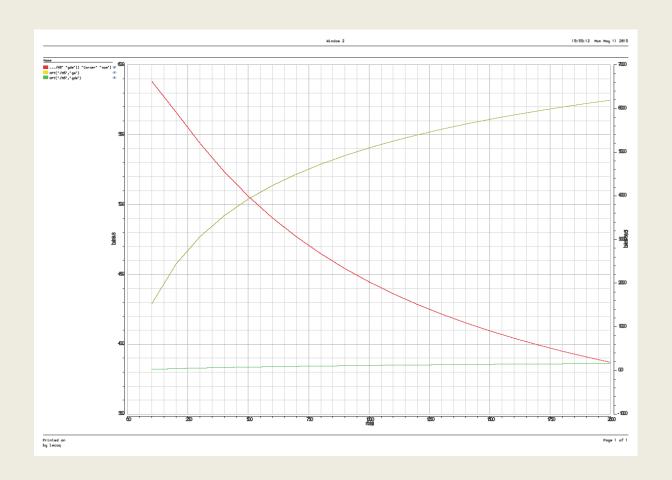

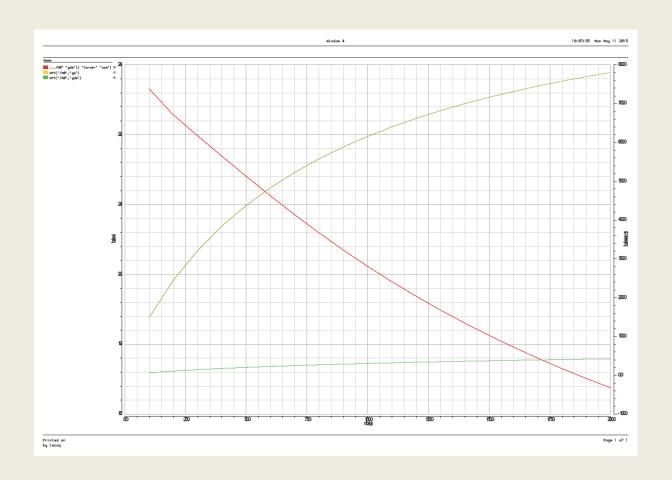

Gm/gds, pour un Nmos dont le L est 2 fois la valeur minimale et w/L=10 Entre 10uA et 200uA:

```

250 == → 125 en AMS 350nm

77 == → 37 en AMS 180nm

58 == → 38 en TSMC 130nm

30 == → 19 en IBM 130nm

22 == → 18 en TSMC 65nm

```

Vcc/Vth pour les Nmos, et les Pmos

```

6 et 4.5 en AMS 350nm

3.6 et 4.2 en AMS 180nm

3.5 et 3.2 en TSMC 130nm

5 et 7.3 en IBM 130nm

2.2 et 2.5 en TSMC 65nm (pour 1.2V)

```

# Gm/gds en AMS 350nm

# Gm/gds en AMS 180 nm

# Gm/gds en tsmc 130nm

# Gm/gds en IBM 130 nm

# Gm/gds en tsmc 65 nm

# Gm/gds en ibm 130 nm Pour un nfet de 20/700 en jaune et pour un dgnfet de même taille, en rouge

Attention, pour un transistor de petite taille on trouve l'inverse